# Design and Implementation of a Hardware Accelerator for one-Dimensional signal Filtering Operations

**Konstantinos Koutropoulos**

June 2014

Dissertation submitted in partial fulfilment for the degree of Master of Science in *Communication & Information Systems*

Department of Informatics & Communications TEI of Central Macedonia

## Abstract

The objective of this thesis is the design of a low-pass Finite Impulse Response filter using hardware description language for FPGA implementation. The window design method was followed and the filter was described in VHDL. The design tool used for the synthesis of the filter is Quartus II v. 9.1 by Altera. Modelsim by Mentor Graphics was used for simulation, in order to verify the filter operation and the accuracy of the results. The comparison with a software-based implementation of the same filter demonstrates that the filter meets the requirements.

Bottom-up hierarchical design was used. The various components were first described in VHDL and then they were instantiated in order to produce the top design entity of the filter. Such filter components that need description are the shift register for the creation of the convolution window, the ROM stage where the filter coefficients are stored, the computationally demanding parallel multiplication stage and finally, the accumulation and normalization stage, where the output sample is computed. Specifications for the necessary data types were defined and alternative implementations of specific stages were tested, as a means to establish best design methodology.

We find that a filter with 101 coefficients can reproduce the original double precision filter specifications using just 14% of the resources of a Cyclone II EP2C35 low cost FPGA device. Also, it can achieve a maximum clock frequency of 50 MHz.

## Attestation

I understand the nature of plagiarism, and I am aware of the University's policy on this.

I certify that this dissertation reports original work by me.

Signature

Date

## Acknowledgements

I would like to thank my supervisor Dr. John Kalomiros for his guidance and assistance during the elaboration of this thesis. I would also like to thank my family for their patience and support.

## Table of Contents

| Abstract                                           | i            |

|----------------------------------------------------|--------------|

| Attestation                                        | ii           |

| Acknowledgements                                   | iii          |

| List of Figures                                    | viii         |

| List of Tables                                     | xii          |

| 1 Introduction                                     |              |

| 1.1 Background and Context                         |              |

| 1.2 Scope and Objectives                           |              |

| 1.3 Achievements                                   |              |

| 1.4 Overview of Dissertation                       |              |

| 2 State-of-The-Art                                 |              |

| 3 Digital Filters                                  |              |

| 3.1 Introduction                                   |              |

| 3.2 Describing Systems                             |              |

| 3.2.1 Time Domain Response                         |              |

| 3.2.2 Frequency Domain Response $H(j\Omega)$       |              |

| 3.2.3 System Function H(s)                         |              |

| 3.2.3.1 Poles and Zeros                            |              |

| 3.3 Filter specifications                          |              |

| 3.3.1 Types                                        |              |

| 3.3.1.1 Low-pass Filter                            |              |

| 3.3.1.2 High-pass Filter                           |              |

| 3.3.1.3 Band-pass Filter                           |              |

| 3.3.1.4 Band-stop or Band-reject Filter            |              |

| 3.3.2 Specifying Magnitude Response                |              |

| 3.3.2.1 Pass-band Cut-off Frequency $F_P$          |              |

| 3.3.2.2 Pass-band Ripple                           |              |

| 3.3.2.3 Stop-band Ripple                           |              |

| 3.3.2.4 Stop-band Cut-Off Frequency                |              |

| 3.3.3 Specifying phase response                    |              |

| 3.4 Describing Discrete Time Signals and Systems . |              |

| 3.4.1 Sampling Frequency                           |              |

| 3.4.2 Discrete Time signals in Time and Frequency  |              |

| 3.4.3 Discrete Time systems in Time and Frequence  | cy domain 15 |

| 3.4.4 The System Function H(z)                             |    |

|------------------------------------------------------------|----|

| 3.4.5 The Difference Equations and H(z)                    |    |

| 3.5 FIR Filters                                            |    |

| 3.5.1 Convolution                                          | 19 |

| 3.5.2 An elementary form of an FIR filter                  |    |

| 3.5.3 Symmetry in FIR Filters                              |    |

| 3.5.4 Windowing                                            |    |

| 3.5.5 Structures for FIR Filters                           |    |

| 3.5.5.1 Direct-form filter structure                       |    |

| 3.5.5.2 Symmetric direct-form filter structure             |    |

| 3.5.5.3 Transposed direct-form structure                   |    |

| 3.6 IIR Filters                                            |    |

| 3.6.1 IIR filter design process                            |    |

| 3.6.2 Indirect Design Method                               |    |

| 3.6.2.1 Analog Filter Prototypes                           |    |

| 3.6.2.2 Mapping from s to z                                |    |

| 3.7 FIR versus IIR Filters                                 |    |

| 4 VHDL                                                     |    |

| 4.1 Introduction                                           |    |

| 4.2 The process of implementing logic circuits – EDA tools |    |

| 4.3 Code Structure-Fundamental VHDL Units                  | 41 |

| 4.3.1 Generic declarations                                 |    |

| 4.4 VHDL objects                                           |    |

| 4.4.1 SIGNALS                                              |    |

| 4.4.2 VARIABLES                                            |    |

| 4.4.3 CONSTANTS                                            | 44 |

| 4.5 Data Types                                             | 44 |

| 4.5.1 Predefined data types                                | 44 |

| 4.5.1.1 Basic predefined data types (package standard)     | 44 |

| 4.5.1.2 Standard-Logic Data Types (Package std_logic_1164) |    |

| 4.5.1.3 Unsigned and Signed Data Types                     |    |

| 4.5.2 User-Defined Data Types                              | 47 |

| 4.5.2.1 Arrays                                             |    |

| 4.5.2.2 Records                                            |    |

| 4.5.2.3 Port Array                                         |    |

| 4.5.2.4 Data Conversion                                    |    |

| 4.6 Operators and Attributes                               |    |

|   | 4.   | 6.1 Assignment operators                      | . 48 |

|---|------|-----------------------------------------------|------|

|   | 4.   | 6.2 Logical Operators                         | . 49 |

|   | 4.   | 6.3 Arithmetic operators                      | . 49 |

|   | 4.   | 6.4 Relational operators                      | . 50 |

|   | 4.   | 6.5 Shift operators                           | . 50 |

|   | 4.   | 6.6 Concatenation operators                   | . 51 |

|   | 4.7  | Attributes                                    | . 51 |

|   | 4.8  | Concurrent and Sequential codes               | . 52 |

|   | 4.   | 8.1 Concurrent Code                           | . 52 |

|   |      | 4.8.1.1 SELECT statement                      | . 52 |

|   |      | 4.8.1.2 WHENELSE statement                    | . 52 |

|   |      | 4.8.1.3 GENERATE statement                    | . 53 |

|   | 4.   | 8.2 Sequential code                           | . 53 |

|   |      | 4.8.2.1 PROCESS                               | . 53 |

|   |      | 4.8.2.2 IF statement                          | . 54 |

|   |      | 4.8.2.3 WAIT statement                        | . 54 |

|   |      | 4.8.2.4 CASE statement                        | . 55 |

|   |      | 4.8.2.5 LOOP statement                        | . 55 |

|   | 4.9  | Components                                    | . 55 |

|   | 4.10 | Simulation (VHDL Test benches)                | . 57 |

|   | 4.   | 10.1Simulation Types                          | . 57 |

| 5 | Ger  | nerating the Filter Coefficients              | . 60 |

|   | 5.1  | Introduction                                  | . 60 |

|   | 5.2  | FDATool                                       | . 60 |

|   | 5.3  | Designing the FIR filter                      | . 61 |

| 6 | Imp  | plementation in Hardware Description Language | . 65 |

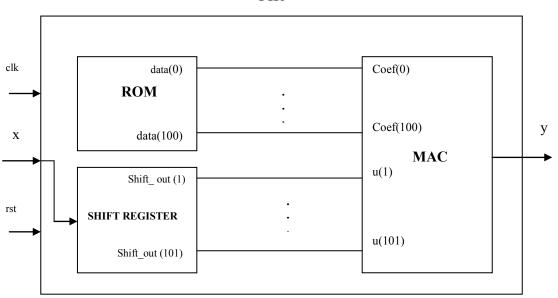

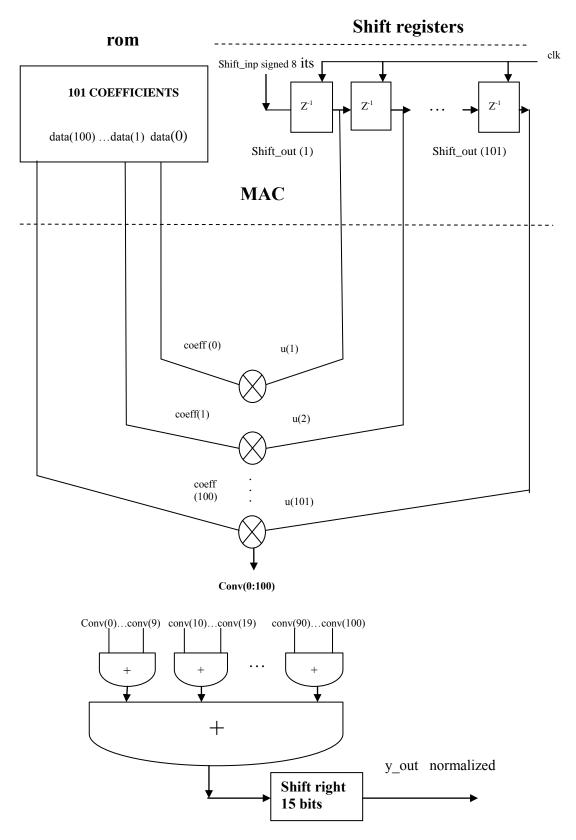

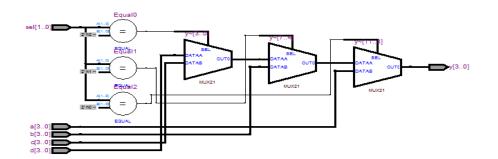

|   | 6.1  | Diagram of the filter                         | . 65 |

|   | 6.2  | Internal parts of the implemented filter      | . 65 |

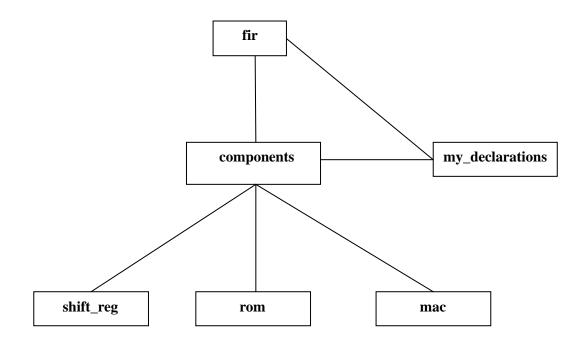

|   | 6.3  | Entities Hierarchy Diagram                    | . 68 |

| 7 | Sim  | nulation - Results                            | . 71 |

|   | 7.1  | Simulation                                    | . 71 |

|   | 7.2  | Results                                       | . 71 |

| 8 | Cor  | nelusions                                     | . 89 |

|   | 8.1  | Summary                                       | . 89 |

|   | 8.2  | Evaluation                                    | . 89 |

|   | 8.3  | Future Work                                   | . 93 |

| R | EFEI | RENCES                                        | . 94 |

| Append | dix A VHDL Code                                       |     |

|--------|-------------------------------------------------------|-----|

| Append | dix B ModelSim Tutorial                               | 104 |

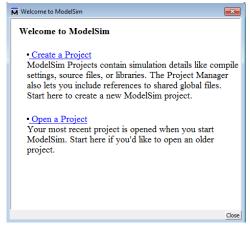

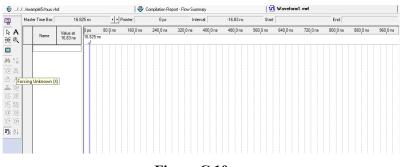

| B.1    | Introduction                                          | 104 |

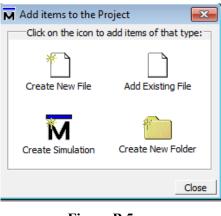

| B.2    | Creating a Project                                    | 104 |

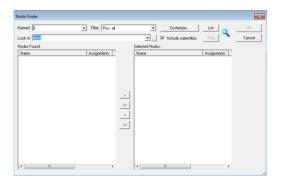

| B.3    | Compiling Project Files                               | 109 |

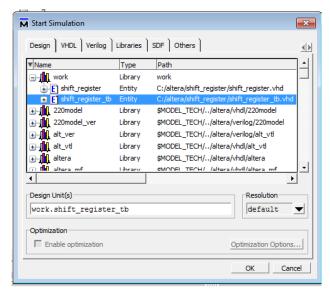

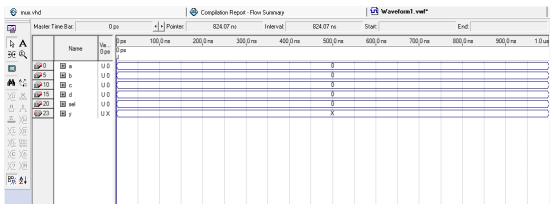

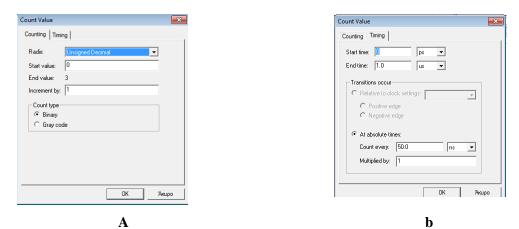

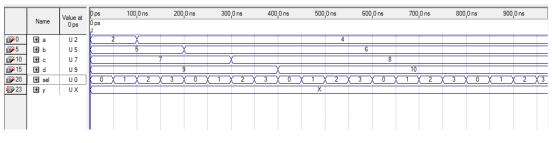

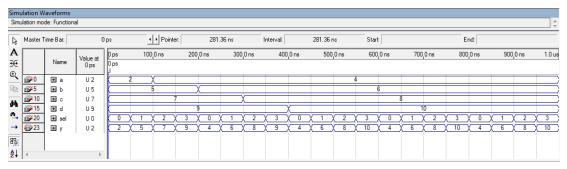

| B.4    | Running a Functional Simulation                       | 110 |

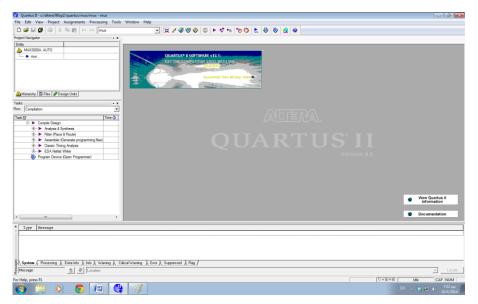

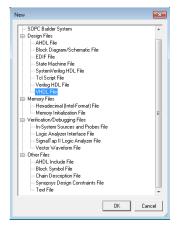

| Append | dix C Quartus II Tutorial                             | 113 |

| C.1    | Introduction                                          | 113 |

| C.2    | Creating a Project                                    | 114 |

| C.3    | Synthesizing the Design                               | 115 |

| C.4    | Simulating the Circuit                                | 118 |

| Append | dix D Read and Store files for simulation             | 121 |

| D.1    | Read and Store files for simulation                   | 121 |

| Append | dix E Design and Test Files for functional simulation | 124 |

| E.1 I  | Design File and Test File                             | 124 |

| Append | dix F Matlab                                          | 127 |

| F.1 S  | Simulation using Matlab                               | 127 |

| F.2 C  | Convert coefficients to integer                       | 128 |

## **List of Figures**

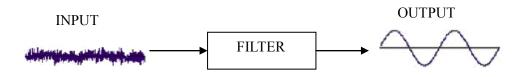

| Figure 3.1  | Basic idea of a filter                                                  | 4  |

|-------------|-------------------------------------------------------------------------|----|

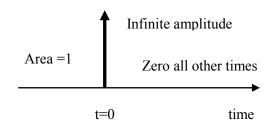

| Figure 3.2  | The impulse signal $\delta(t)$                                          | 5  |

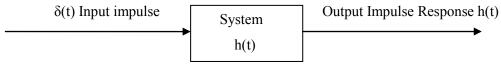

| Figure 3.3  | A system in the time domain                                             | 6  |

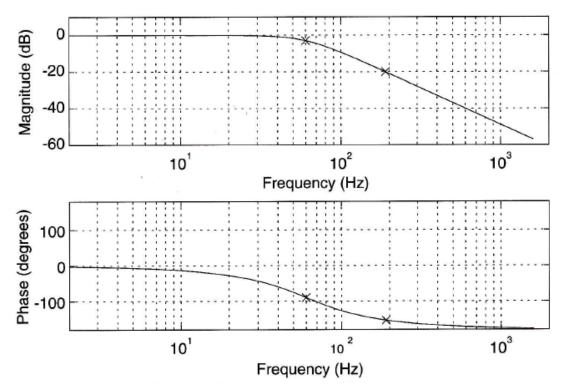

| Figure 3.4  | Frequency and phase response of a low-pass filter                       | 6  |

| Figure 3.5  | The s – plane                                                           | 7  |

| Figure 3.6  | Magnitude response of low-pass filter                                   | 9  |

| Figure 3.7  | Magnitude response of High-pass Filter                                  | 10 |

| Figure 3.8  | Magnitude response of Band-pass Filter                                  | 10 |

| Figure 3.9  | Magnitude response of Band-stop Filter                                  | 11 |

| Figure 3.10 | Low-pass analog filter parameters                                       | 12 |

| Figure 3.11 | Low-pass digital filter parameters                                      | 12 |

| Figure 3.12 | Linear phase response of a low-pass filter                              | 13 |

| Figure 3.13 | Analog and Discrete time signal                                         | 14 |

| Figure 3.14 | The z – plane                                                           | 16 |

| Figure 3.15 | IIR filter structure                                                    | 18 |

| Figure 3.16 | FIR structure                                                           | 19 |

| Figure 3.17 | Relationship between impulse response and coefficients of an FIR filter | 20 |

| Figure 3.18 | A four tapped filter                                                    | 22 |

| Figure 3.19 | The output y(n)                                                         | 22 |

| Figure 3.20 | Magnitude response using equal coefficients                             | 23 |

| Figure 3.21 | Magnitude response using individual weights of coefficients             | 23 |

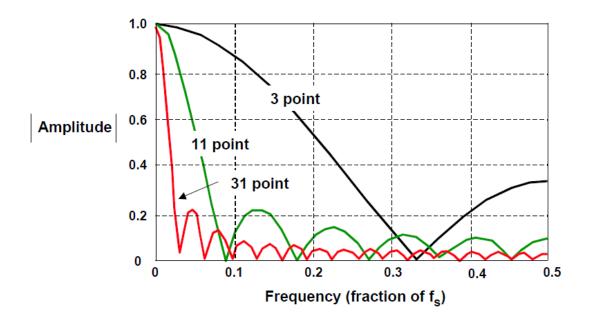

| Figure 3.22 | Improvement of sharpness of the roll-off in the transition area         | 24 |

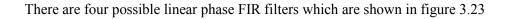

| Figure 3.23 | Symmetry in FIR Filters                                                 | 24 |

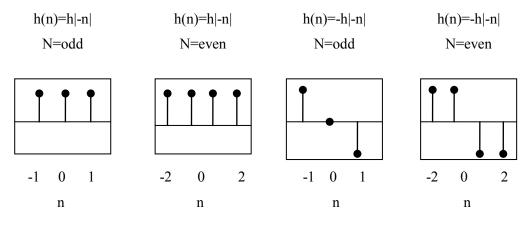

| Figure 3.24 | Impulse response of an ideal low-pass filter                            | 26 |

| Figure 3.25 | Truncated ideal low-pass filter impulse response                        | 27 |

| Figure 3.26 | Magnitude response using 21 coefficients                                | 27 |

| Figure 3.27 | Magnitude response using twice as many coefficients as in figure 3.26   | 28 |

| Figure 3.28 | Smoothing the truncated impulse response.                               | 28 |

| Figure 3.29 | Magnitude response using windowed coefficients                          | 29 |

| Figure 3.30 | Time domain and magnitude response of some common windows               | 31 |

| Figure 3.31 | A 4-tap filter implemented in direct-form                               | 32 |

| Figure 3.32 | A 4-tap FIR filter using the symmetric direct-form                      | 33 |

| Figure 3.33 | A 4-tap FIR Filter using the transposed direct-form                     | 33 |

| Figure 3.34 | Direct I form of an IIR filter                                          | 34 |

| Figure 3.35 | Regions of stable poles in the s-plane and z-plane                      | 36  |

|-------------|-------------------------------------------------------------------------|-----|

| Figure 4.1  | Design Flow                                                             | 40  |

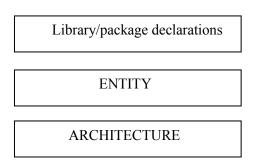

| Figure 4.2  | Fundamental sections of a VHDL code                                     | 41  |

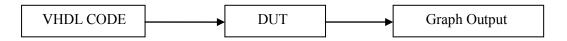

| Figure 4.3  | Type I test bench                                                       | 57  |

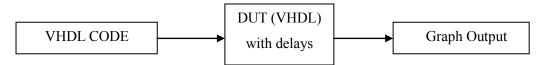

| Figure 4.4  | Type II test bench                                                      | 57  |

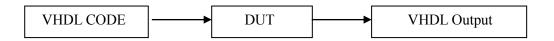

| Figure 4.5  | Type III test bench                                                     | 58  |

| Figure 4.6  | Type IV test bench (full bench)                                         | 58  |

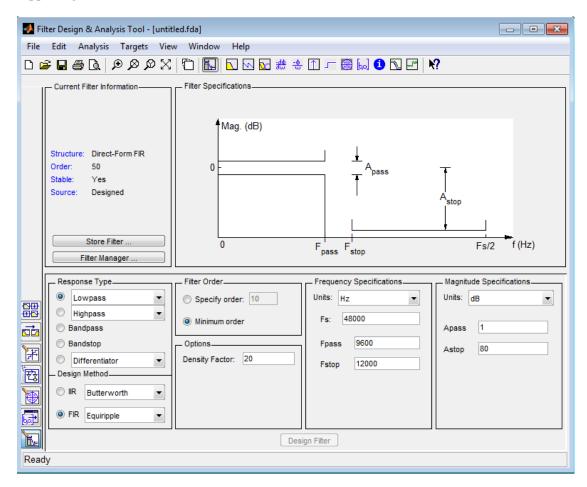

| Figure 5.1  | Graphical User Interface                                                | 61  |

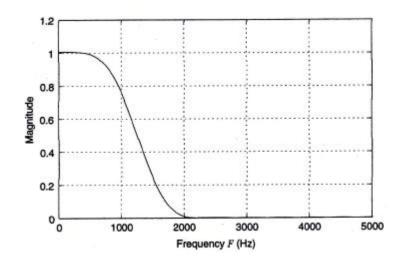

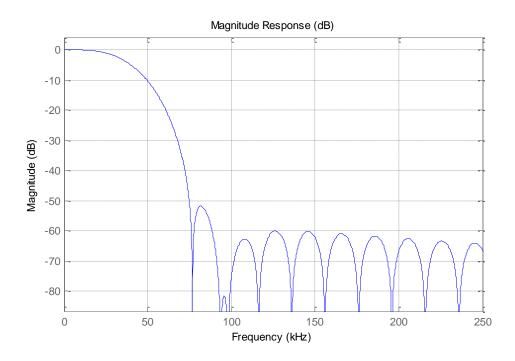

| Figure 5.2  | Frequency response of the filter                                        | 63  |

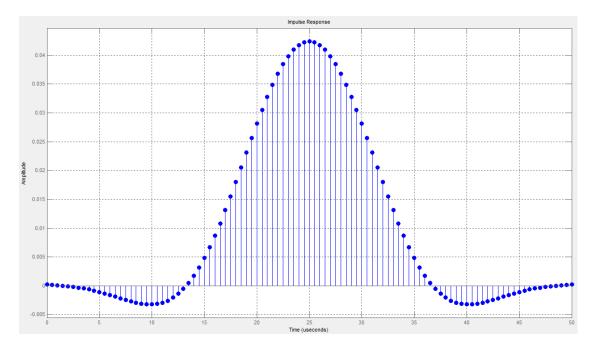

| Figure 5.3  | Impulse response of the filter                                          | 63  |

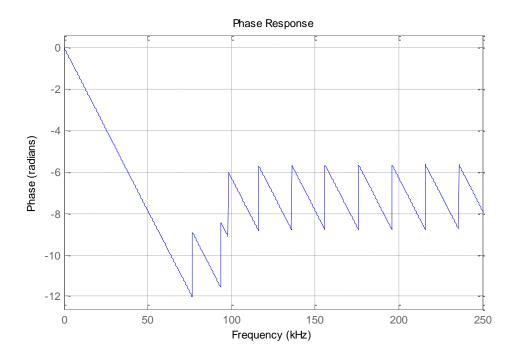

| Figure 5.4  | Linear phase in the pass-band area                                      | 64  |

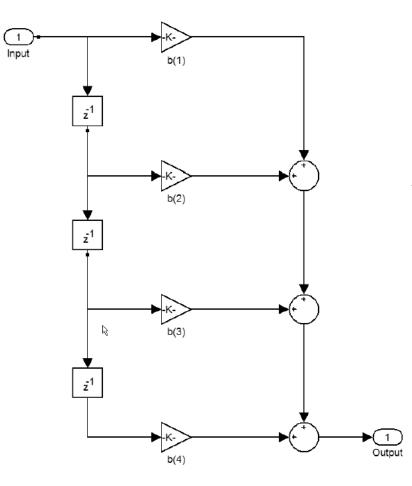

| Figure 6.1  | Diagram of the FIR                                                      | 65  |

| Figure 5.2  | Internal parts of the implemented filter                                | 67  |

| Figure 6.3  | Entities Hierarchy Diagram                                              | 68  |

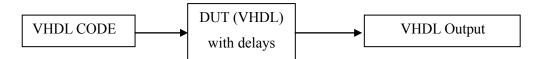

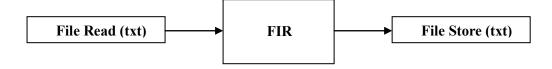

| Figure 7.1  | Procedure for simulation                                                | 71  |

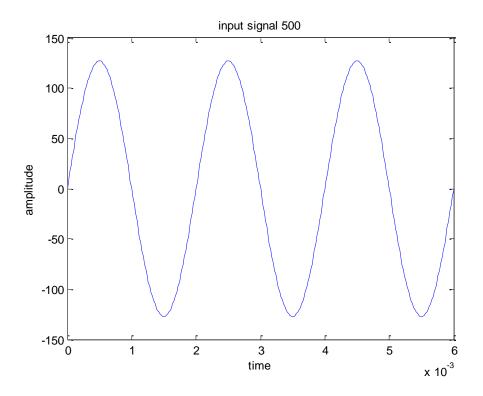

| Figure 7.2  | Input signal 500 Hz                                                     | 72  |

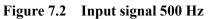

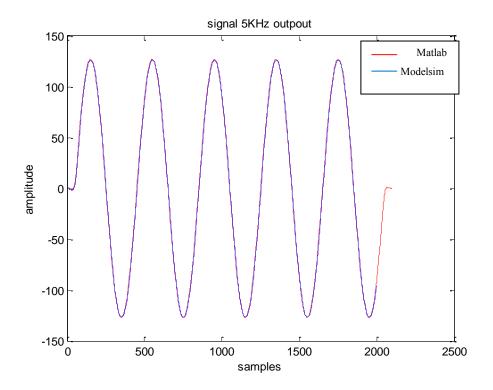

| Figure 7.3  | Comparison between the filter output based on Matlab implementation and | the |

| output      | from the VHDL hardware model (Modelsim)                                 | 72  |

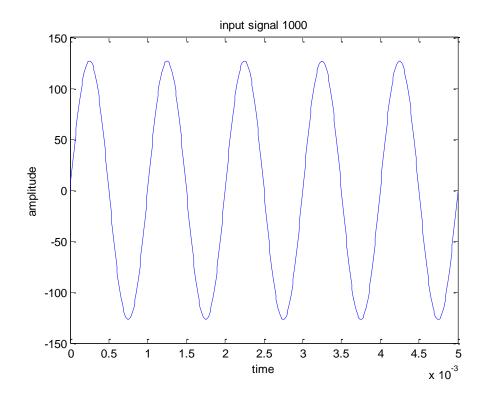

| Figure 7.4  | Input signal 1KHz                                                       | 73  |

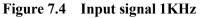

| Figure 7.5  | Comparison between the filter output based on Matlab implementation and | the |

| output      | from the VHDL hardware model (Modelsim)                                 | 73  |

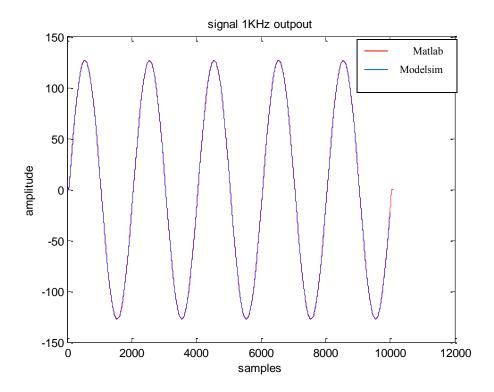

| Figure 7.6  | Input signal 1KHz                                                       | 74  |

| Figure 7.7  | Comparison between the filter output based on Matlab implementation and | the |

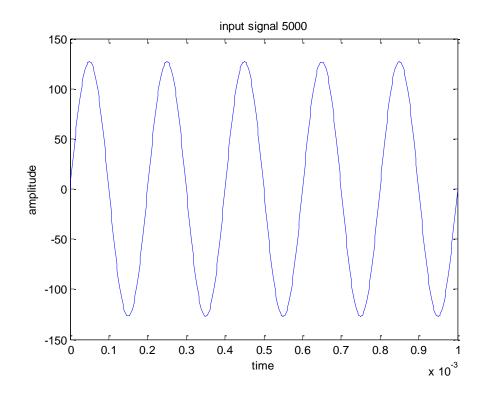

| output      | from the VHDL hardware model (Modelsim)                                 | 74  |

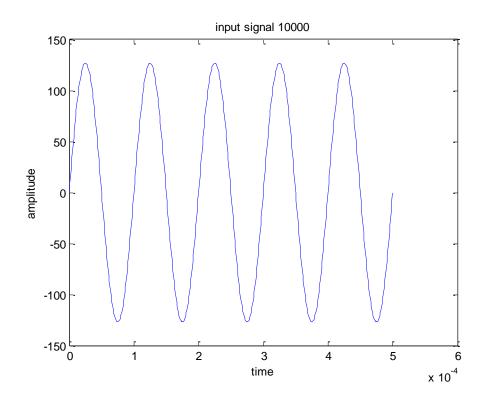

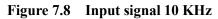

| Figure 7.8  | Input signal 10 KHz                                                     | 75  |

| Figure 7.9  | Comparison between the filter output based on Matlab implementation and | the |

| output      | from the VHDL hardware model (Modelsim)                                 | 75  |

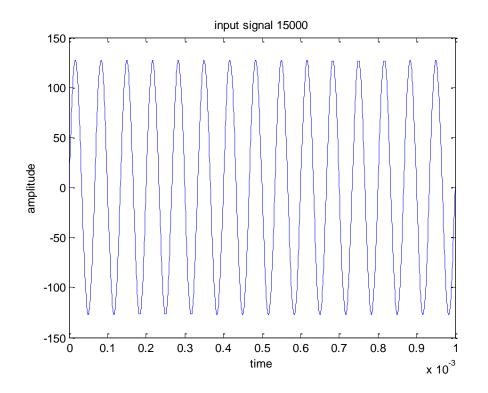

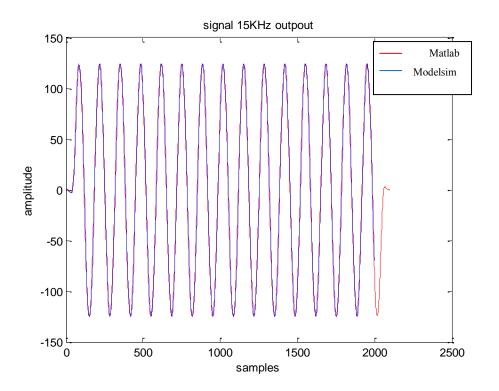

| Figure 7.10 | Input signal 15 KHz                                                     | 76  |

| Figure 7.11 | Comparison between the filter output based on Matlab implementation and | the |

| output      | from the VHDL hardware model (Modelsim)                                 | 76  |

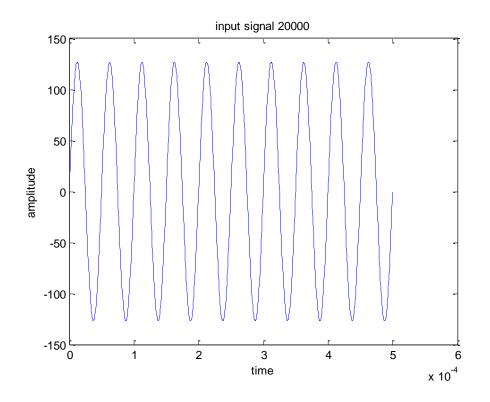

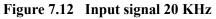

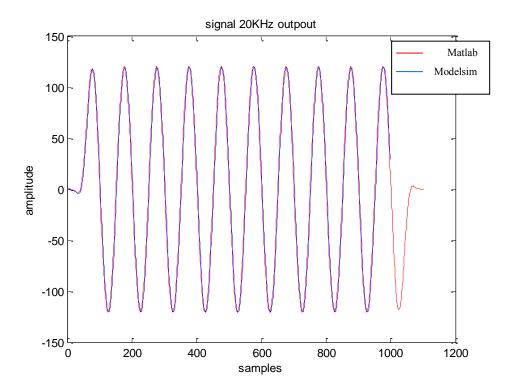

| Figure 7.12 | Input signal 20 KHz                                                     | 77  |

| Figure 7.13 | Comparison between the filter output based on Matlab implementation and | the |

| output      | from the VHDL hardware model (Modelsim)                                 | 77  |

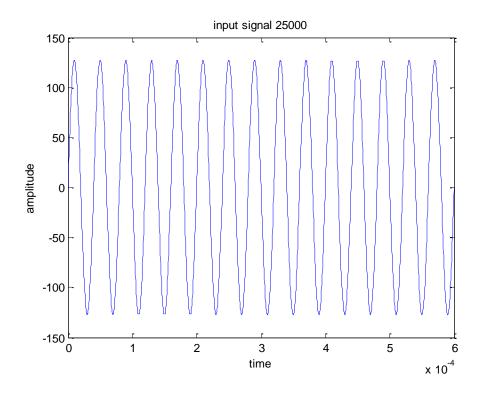

| Figure 7.14 | Input signal 25 KHz                                                     | 78  |

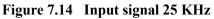

| Figure 7.15 | Comparison between the filter output based on Matlab implementation and | the |

| output      | from the VHDL hardware model (Modelsim)                                 | 78  |

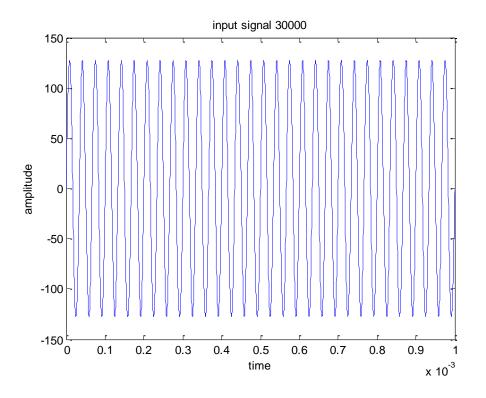

| Figure 7.16 | Input signal 30 KHz                                                     | 79  |

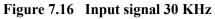

| Figure 7.17 | Comparison between the filter output based on Matlab implementation and | the  |

|-------------|-------------------------------------------------------------------------|------|

| output      | from the VHDL hardware model (Modelsim)                                 | 79   |

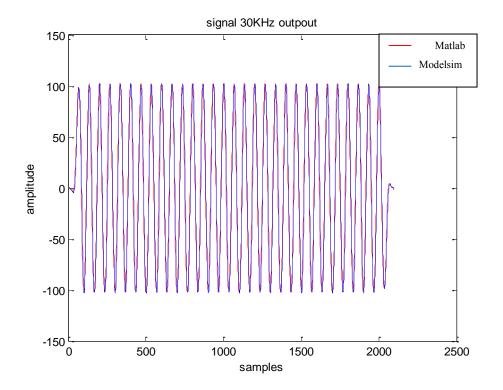

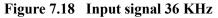

| Figure 7.18 | Input signal 36 KHz                                                     | 80   |

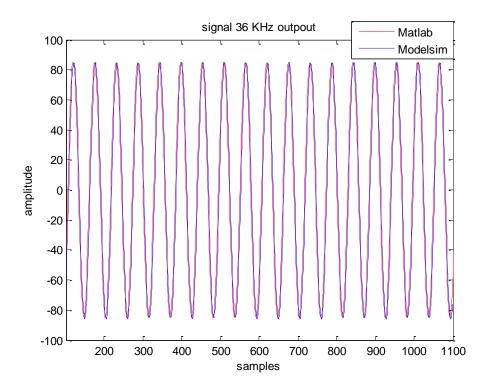

| Figure 7.19 | Comparison between the filter output based on Matlab implementation and | the  |

| output      | from the VHDL hardware model (Modelsim)                                 | 80   |

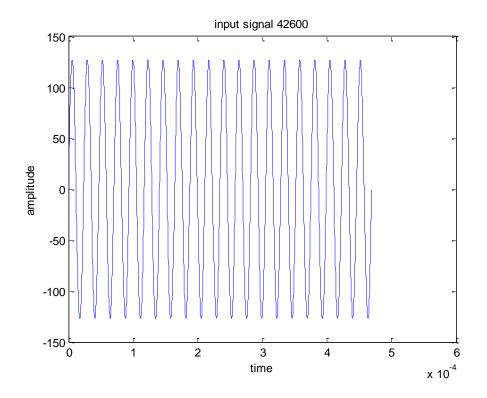

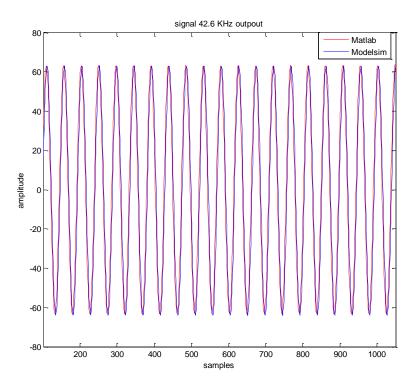

| Figure 7.20 | Input signal 42.6 KHz                                                   | 81   |

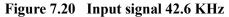

| Figure 7.21 | Comparison between the filter output based on Matlab implementation and | the  |

| output      | from the VHDL hardware model (Modelsim)                                 | 81   |

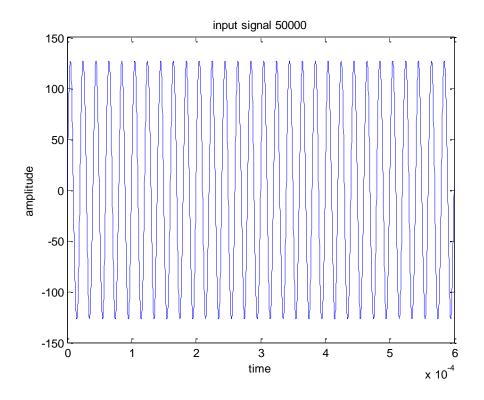

| Figure 7.22 | Input signal 50 KHz                                                     | 82   |

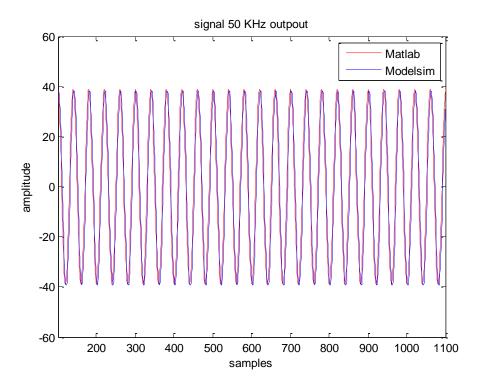

| Figure 7.23 | Comparison between the filter output based on Matlab implementation and | the  |

| output      | from the VHDL hardware model (Modelsim)                                 | 82   |

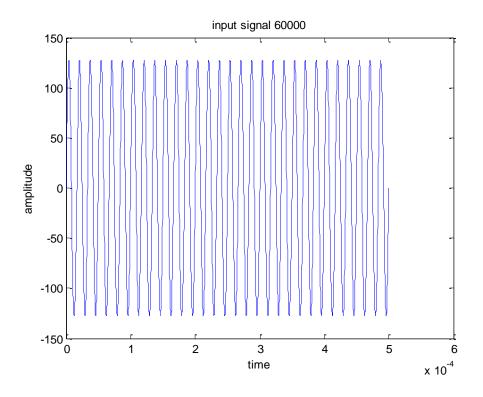

| Figure 7.24 | Input signal 60 KHz                                                     | 83   |

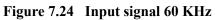

| Figure 7.25 | Comparison between the filter output based on Matlab implementation and | the  |

| output      | from the VHDL hardware model (Modelsim)                                 | 83   |

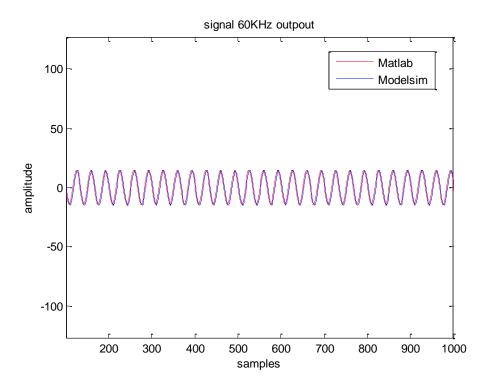

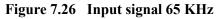

| Figure 7.26 | Input signal 65 KHz                                                     | 84   |

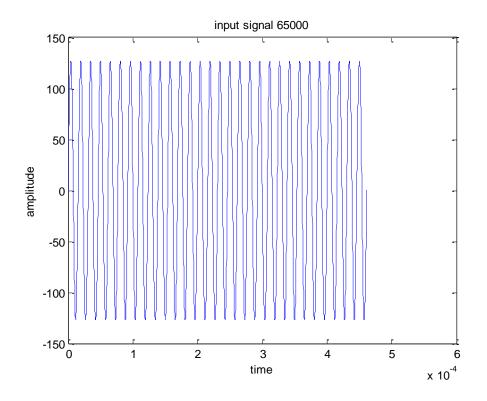

| Figure 7.27 | Comparison between the filter output based on Matlab implementation and | the  |

| output      | from the VHDL hardware model (Modelsim)                                 | 84   |

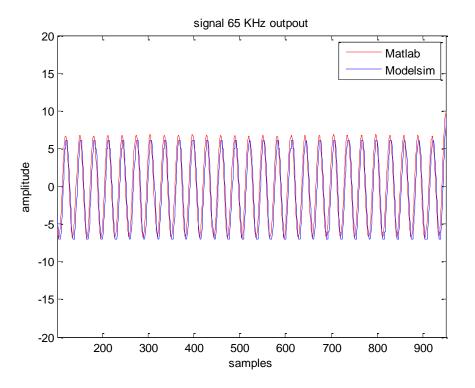

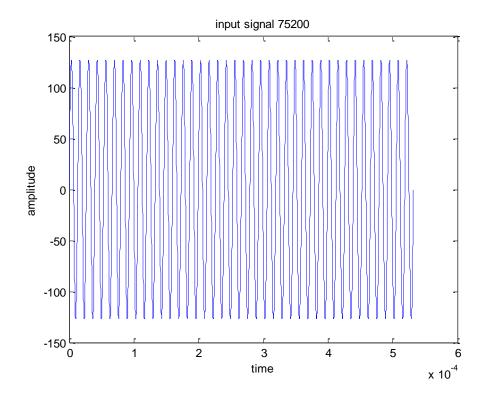

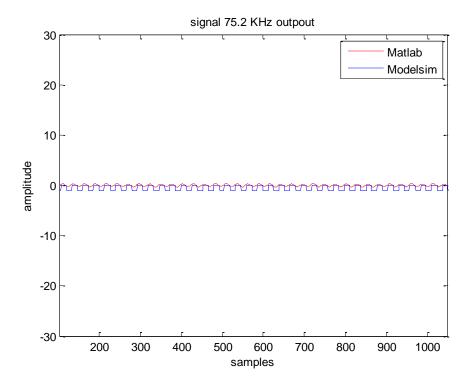

| Figure 7.28 | Input signal 75.2 KHz                                                   | 85   |

| Figure 7.29 | Comparison between the filter output based on Matlab implementation and | the  |

| output      | from the VHDL hardware model (Modelsim)                                 | 85   |

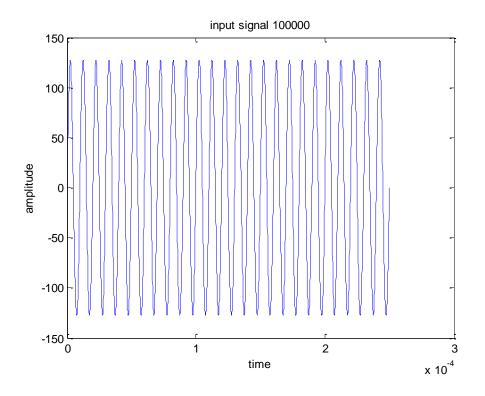

| Figure 7.30 | Input signal 100 KHz                                                    | 86   |

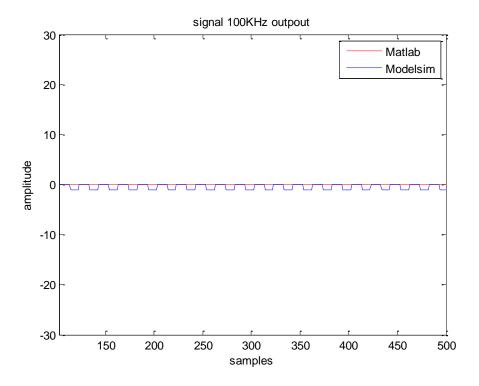

| Figure 7.31 | Comparison between the filter output based on Matlab implementation and | the  |

| output      | from the VHDL hardware model (Modelsim)                                 | 86   |

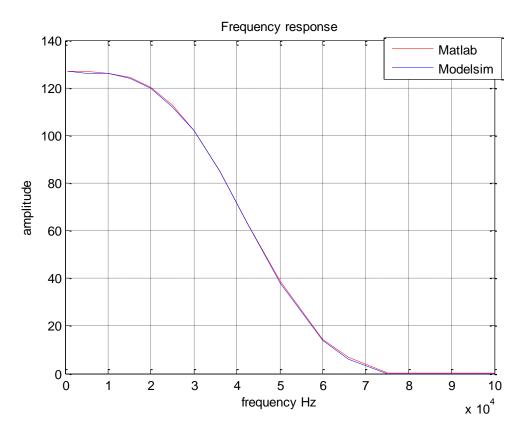

| Figure 7.32 | Diagram of the filter frequency response                                | 88   |

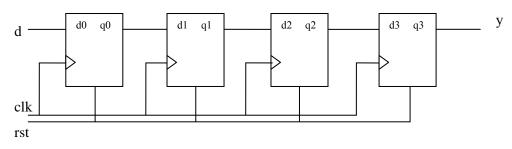

| Figure 8.1  | A 4-tap filter implemented in direct-form                               | 90   |

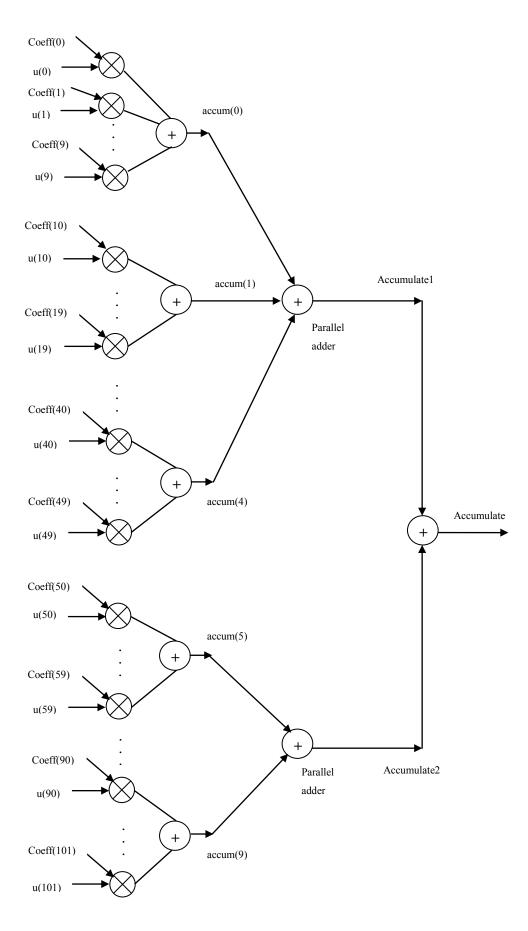

| Figure 8.2  | parallel accumulator                                                    | 92   |

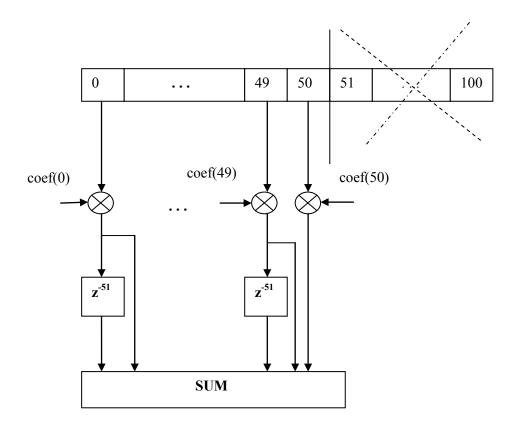

| Figure 8.1  | Linear phase filter with reduced number of multipliers                  | 93   |

| Figure B.1  |                                                                         | .104 |

| Figure B.2  |                                                                         | .105 |

| Figure B.3  |                                                                         | .105 |

| Figure B.4  |                                                                         | .105 |

| Figure B.5  |                                                                         | .106 |

| Figure B.6  |                                                                         | .106 |

| Figure B.7  |                                                                         | .106 |

| Figure B.8  |                                                                         | .108 |

| Figure B.9  |                                                                         | .109 |

| Figure B.10 |                                                                         | .109 |

| Figure B.11 | 110 |

|-------------|-----|

| Figure B.12 | 110 |

| Figure B.13 | 111 |

| Figure B.14 | 111 |

| Figure B.15 | 112 |

| Figure B.16 | 112 |

| Figure B.17 | 112 |

| Figure C.1  | 113 |

| Figure C.2  | 114 |

| Figure C.3  | 114 |

| Figure C.4  | 115 |

| Figure C.5  | 115 |

| Figure C.6  | 116 |

| Figure C.7  | 117 |

| Figure C.8  | 117 |

| Figure C.9  | 117 |

| Figure C.10 | 118 |

| Figure C.11 | 118 |

| Figure C.12 | 119 |

| Figure C.13 | 119 |

| Figure C.14 | 120 |

| Figure C.15 | 120 |

| Figure C.16 | 120 |

## List of Tables

| Table 3.1 | Ideal impulse responses for common filter types                          | 25 |

|-----------|--------------------------------------------------------------------------|----|

| Table 3.2 | Key properties of windows                                                | 30 |

| Table 4.1 | Main type conversion options                                             | 49 |

| Table 4.2 | Shift operators and their functions                                      | 50 |

| Table 4.3 | Pre-defined data attributes                                              | 51 |

| Table 4.4 | Signal attributes                                                        | 51 |

| Table 5.1 | Filter coefficients as integers                                          | 64 |

| Table 7.1 | Frequency response using the Matlab software Model and the hardware mode | l, |

|           | simulated in Modelsim                                                    | 87 |

| Table 8.1 | Recourse Requirements                                                    | 89 |

## **1** Introduction

### 1.1 Background and Context

Hardware accelerators are specific-processor systems designed to implement computationally intensive operations at high processing rates. Instead of executing sequential commands they perform parallel data processing, unfolding the sequential loop into a pipelined data path.

In this thesis a digital filter was designed by implementing the basic Multiply-Accumulate operation as a hardware component on-a-chip. The convolution process was parallelized using shift registers. The filter coefficients were hardwired in on-chip ROM memory, in the form of a look-up table. Also the specifications of the filter were set. A low-pass filter with  $F_c = 35$  KHz (-3dB) was designed (see details in paragraph 5.3).

First, a software model of the specific filter was implemented using the Matlab programming environment in order to verify the results which were produced by the hardware.

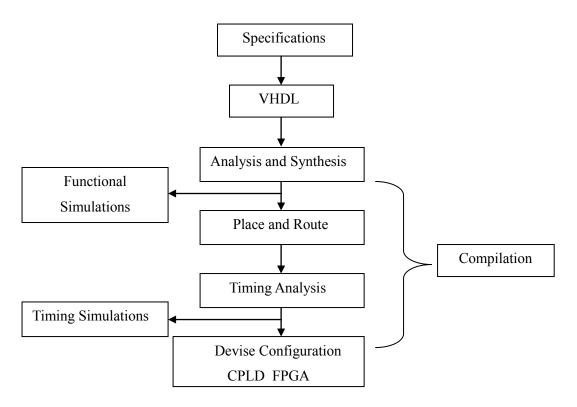

Second, the hardware system was designed in VHDL hardware description language, using software tools like Quartus II by Altera for synthesis and Modelsim by Mentor Graphics for simulation.

### 1.2 Scope and Objectives

The objective of this work is to establish best design rules for the hardware implementation of a FIR filter and create a detailed description of the filter design, using the Hardware Description Language VHDL. The design is assessed in terms of the required hardware resources and the maximum operating frequency. Also, it is assessed in terms of accuracy, by comparing the results of a software implementation of the same filter, using double precision variables and floating point computations.

As a methodology, bottom-up hierarchical design is used, in which the various components are first described in VHDL and then they are instantiated in order to produce the top design entity of the filter. Such filter components that need description are the shift register for the creation of the convolution window, the ROM stage which keeps the filter coefficients, the computationally demanding parallel multiplication stage, and finally the accumulation and normalization stage, where the output sample is computed. Specifications for the necessary data types were defined. Alternative implementations of specific stages were tested, using different bit-widths and accumulation techniques, as a means to establish best design methodology.

Test-benches were designed for the simulation of the filter. For this purpose we use VHDL test code that reads signals stored in text files. The simulation is performed with ModelSim and the output is stored in a new text file. Then, the results can be compared with the expected waveforms.

## 1.3 Achievements

The design is assessed using as a measure the resource requirements for the overall implementation of the filter in a medium FPGA device, like the Cyclone II EP2C35. In addition, the timing analysis results provide a measure of the performance of the design, when it is implemented in the above FPGA device. We find that a filter with 101 coefficients can reproduce adequately the original double precision filter specifications using just 4677 logic elements including logic registers. This represents 14% of the resources of a low cost FPGA device. Also, it can achieve a maximum clock frequency of 50 MHz.

## 1.4 Overview of Dissertation

In chapter 3 there is a presentation of digital filters. In particular, the Finite Impulse Response Filters and the window design method are described. In Chapter 4, the Hardware Description Language VHDL is presented. At the end of the chapter, the simulation with VHDL test benches is described, which is one of the most crucial steps in VHDL circuit design. In Chapter 5, the procedure followed for the generation of the filter coefficients is analyzed, using the Graphical User Interface Filter Design and Analysis Tool (FDATool). In Chapter 6, the description of the hierarchical design of the filter is given. In Chapter 7, the results that were derived by the programming environment Matlab and the simulator Modelsim are presented and compared. Finally, in Chapter 8, the achievements and the conclusions of this thesis are presented. Also, a possible future development of this work is proposed.

## 2 State-of-The-Art

Signal processing has been used to transform or manipulate analog or digital signals. Digital signal processing has found many applications like filtering and convolution, Fourier transform, audio processing, image processing, information systems and i.e.

Digital signal processing is a mature technology and has replaced analog signal processing systems in many applications. Compared to analog systems, digital signal processing systems has several advantages, like the insensitivity to change in temperature, aging or component tolerance. Two events have accelerated DSP development [4]. The first was the disclosure by Cooley and Tuckey of an efficient algorithm to compute the discrete Fourier Transform and the second was the introduction of programmable digital signal processor (PDSP).

Programmable digital signal processors have enjoyed tremendous success for the last two decades [4]. They are based on a reduced instruction set computer (RISC) with an architecture consisting of at least one fast array multiplier with an extended word width accumulator. The PDSP advantage comes from the fact that most signal processing algorithms are multiply and accumulate intensive.

Now, Field-programmable gate arrays (FPGAs) are on the verge of revolutionizing digital signal processing in the manner that PDSP did two decades ago [4]. Many digital signal processing algorithms such as FFTs, FIR or IIR filters which built by PDSPs are now replaced by FPGAs. Many high-bandwidth signal processing applications such as wireless, multimedia or satellite transmission can be found today, and FPGA technology can provide more bandwidth through multiple MAC on one chip. Also compared to PDSPs, FPGA design exploits parallelism e.g., implementing multiple multiply-accumulate calls efficiency, e.g., zero product-terms are removed, and pipelining, i.e., each LE has a register, therefore pipelining requires no additional resources [4]. It is assumed that in the future PDSPs will dominate applications that require complicated algorithms, while FPGAs will dominate more frond-end applications like FIR filters, CORDIC algorithms, or FFTs.

Another trend in the DSP hardware design is the migration from graphical design entries to hardware description language. It has been found that code reuse is much higher with hardware description language than with graphical design entries. Two hardware description languages are popular today. The US west cost and Asia prefer Verilog, while US east cost and Europe prefer VHDL. For DSP using FPGA both languages seem to be well suited, although VHDL examples are a little easier to read because of the supported signed arithmetic and multiply/divide operations in the IEEE VHDL 1076-1987 and 1076-1993 standards [4].

## **3** Digital Filters

#### 3.1 Introduction

Digital filtering is one of the most powerful tools of DSP. Digital filters are capable of performance specifications that it would be difficult or impossible to achieve with an analog filter. Moreover the characteristics of a digital filter can be easily changed under software control. Therefore they are widely used in communications and modems [6].

Designing a digital filter requires a procedure that has the same fundamental elements as that for analog filters. First the desired filter response is characterized and the filter parameters are then calculated [6]. That means that characteristics such as the amplitude and phase response are derived in the same way. The fundamental difference between analog and digital filter is instead of calculating capacitor, resistor and inductor values in analog filter, coefficient values are calculated for a digital filter [6]. As a result in digital filter, numbers replace the resistors and the capacitors components of the analog filter. This numbers are stored in a memory as filter coefficients and are used with the input signal (sampled data values) from the ADC (Analog to Digital Converter) to perform the filter calculations.

The function of filtering is the same for analog or digital signal. In signal processing, the function of a filter is to remove unwanted parts of the signal such as random noise, or to extract useful parts of the signal, such as the components lying within a certain frequency range. Figure 3.1 illustrates the basic idea of a filter.

Figure 3.1 Basic idea of a filter

#### 3.2 Describing Systems

In paragraph 3.1 we mentioned that filters are a system that takes an input signal, make some modifications, and produces an output signal [3]. Usually a system has one or more inputs and one or more outputs. The filter as a system has one input signal and one output signal. We know that if we want to describe a signal we use the time domain and the frequency domain. Just like signals, there are the time domain and the frequency domain to describe systems. But a system is not a signal, a system modifies signals. Therefore the only we can do is to describe what a system does to signals which is called system response. Hence we must describe the Time Domain Response and the Frequency Domain Response of a system.

#### 3.2.1 Time Domain Response

The most common way to characterize a system in the time domain is its impulse response. This means that we observe the response of the system (output) to an impulse input.

An impulse is like a spike. The signal is at 0, the impulse width is very small and the amplitude is very large. Mathematically the width is infinitesimally small and the height infinite (see figure 3.2). However if we integrate the signal which is the area under the pulse we will get a total area of 1. The notation for the impulse signal is  $\delta(t)$  and the notation h(t) is used for the impulse response of a system (see Figure 3.3) The most important aspect of the impulse is that excites a system equally at all frequencies [3].

Figure 3.2 The impulse signal  $\delta(t)$

#### **3.2.2** Frequency Domain Response H(jΩ)

For a system (Linear, Time Invariant)  $H(j\Omega)$  describes both the gain and phase shift that a signal of frequency  $\Omega$  experiences when going through a system [3]. The frequency  $\Omega$  is expressed in radians/second.  $H(j\Omega)$  is also called the *transfer function* of the system. As we can observe from the j, the transfer function is complex which means that if we evaluate  $H(j\Omega)$ at some frequencies the result is a complex number which shows the magnitude  $|H(j\Omega)|$  and the phase  $\angle H(j\Omega)$ . The magnitude is the ratio of the magnitude of the output to the magnitude of an input at that frequency and the phase is the difference in phases between the output and input [3]. Example:

We assume that  $H(j\Omega) = 142120/142120 + 533j\Omega - \Omega^2$  is the transfer function of a system. If the input of the system is a sinusoid with magnitude 4 and frequency 60Hz, what is this system output?

First we need to convert from Hertz to radians/sec which is 60 Hz =  $60.2\pi$  rad/sec = 377 rad/sec. This is  $\Omega$ . For the calculations we use complex arithmetic because there is a j in the denominator. Finally H(j $\Omega$ ) = -0.000008 - 0.70729j, or in polar form H(j $\Omega$ ) = 0.70729 [-1.57 (angle is in radians). It is convenient to express the angle in terms of  $\pi$  which is -1.57 rad =  $-\pi/2$ . Therefore the output of this system has a magnitude which is 4x0.70729 = 2.83 and a phase which is different by  $-90^{0}$  from the input signal.

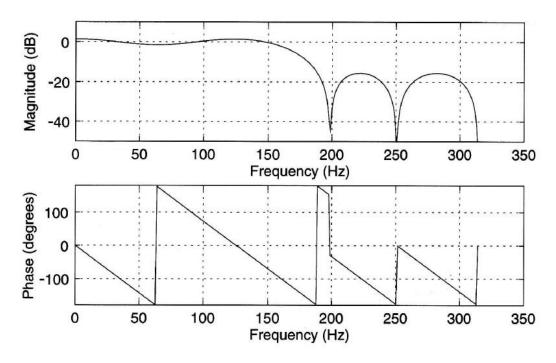

Figure 3.3 A system in the time domain

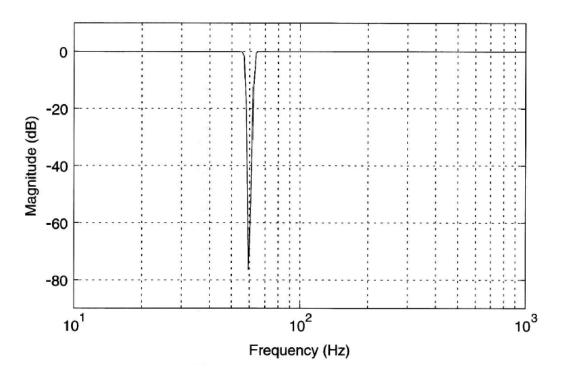

Now if we do the above calculations for different values of frequency and plot the frequency and phase response we will understand the overall behavior of the system. Figure 3.4 [3]) shows the frequency and phase response of the system. We can see from the plots that H(j $\Omega$ ) describes a system that passes lower frequencies with no attenuation, but start attenuating signals above 200Hz. The phase goes through a transition as well approaching  $-\pi$ . Hence the specific H(j $\Omega$ ) describes a low-pass filter.

Figure 3.4 Frequency and phase response of a low-pass filter

#### 3.2.3 System Function H(s)

H(jΩ) provides us with the description of the system and plot of the magnitude response. However, we use a more general description which is called the system function H(s). But which is the difference between H(jΩ) and H(s)? The first function uses the simple frequency Ω while the latter uses the complex frequency s. Signals with complex frequency are sinusoids with exponential growth or decay of the amplitude [3]. Therefore we multiply the sinusoid by the exponential term  $e^{\sigma t}$  to get x(t) = A  $e^{\sigma t} \cos(\Omega t + \theta)$  which is an example of complex frequency. The σ term affects how quickly and in what direction amplitude growth occurs [3]. H(s) can bundle both frequency and the exponential factor into a complex number which called s. Therefore the real part is the exponential growth factor  $\sigma$  while the imaginary part is the frequency  $\Omega$ . Therefore any value of  $s = \sigma + j\Omega$ . Complex frequency is used to represent signals and systems in the *s*-*plane*. The horizontal axis of the s – plane is the real part of s the  $\sigma$ , and the vertical axis of the s – plane is the imaginary part of s the j $\Omega$ . The s – plane is very important because we can describe a system by locating the poles and zeros of the system.

3.2.3.1 Poles and Zeros

H(s) is always of the form

H(s) = \_\_\_\_\_

There are two interesting sets of values for s in this equation. First there are values of s such that the numerator of H(s) is equal to 0. These values of s are the roots of the numerator of H(s) which are the zeros of H(s). Poles are those values of s such that the denominator equals to zero.

Stable filters may have zeros located anywhere in the s-plane. Zeros located on the j $\Omega$  axis completely block signals at that frequency.

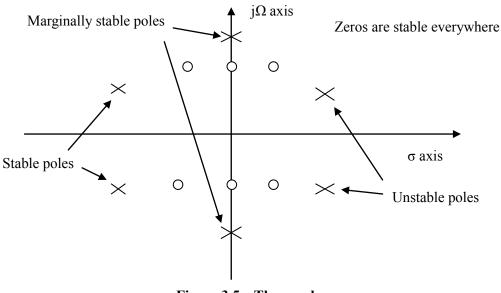

Stable filters may have only poles in the half of the s-plane with  $\sigma < 0$ . Poles on the j $\Omega$  axis correspond to constant oscillation. Poles with  $\sigma > 0$  lead to exponentially increasing outputs and are associated with unstable filters. Figure 3.5 shows poles and zeros in the s-plane.

Figure 3.5 The s – plane

Also the order of a filter corresponds to the maximum number of poles or zeros in a filter whether analog or digital. By adding poles and zeros in a filter we can get smoother pass-band,

lower stop-band gain or steeper transition. In an analog filter we can increase the number of op-amp or the number of capacitors in order to increase the poles and zeros. In a digital filter higher order filter requires more coefficients which mean more multiplications and more memory. The trade off is between how good the filter characteristics are and how much processing time such a filter requires [3]. So filter design is the ability of using a minimum filter order to meet filter design criteria.

#### 3.3 Filter specifications

#### 3.3.1 Types

One way of organizing filters is by their frequency magnitude characteristics. The types of filters are low-pass, high-pass, band-pass and band-stop. [3].

#### 3.3.1.1 Low-pass Filter

The following diagrams show in figures 3.6 - 3.12 are taken from citation [3].

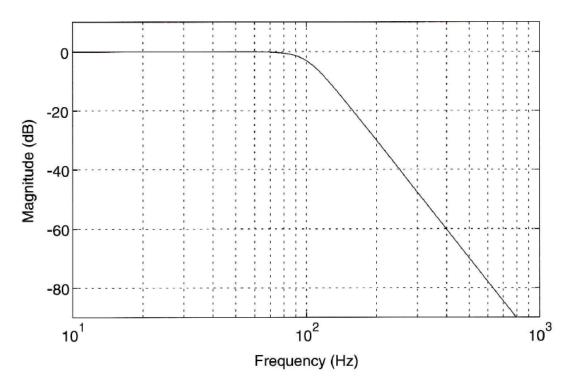

Figure 3.6 shows the magnitude response of a low-pass filter. Frequencies from zero to a specified frequency which called "cut-off frequency" or -3dB frequency are passed with relatively equal magnitude, while higher frequencies are greatly attenuated. Low-pass filter are generally used when the signal of interest is in the range of DC (0Hz) to some frequency, but where other higher frequency signals (like noise) are present [3].

#### 3.3.1.2 High-pass Filter

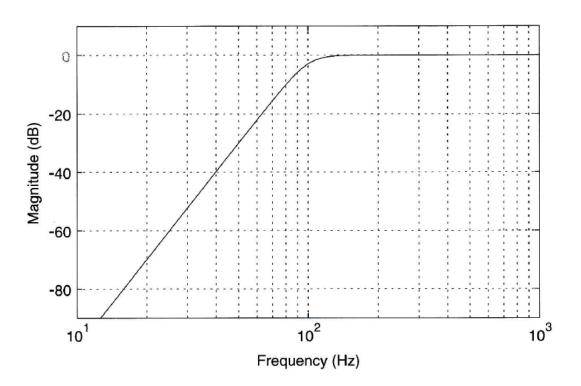

Figure 3.7 shows a high-pass filter magnitude response. This type of filter has ideally infinite attenuation at DC. In reality we must mention that there is a limit on the upper frequency that can be passed. For example the sampling rate of a DSP hardware will set the upper frequency limit in digital filter implementation. For high-pass filters the cut-off frequency is the lower limit of the pass-band.

#### 3.3.1.3 Band-pass Filter

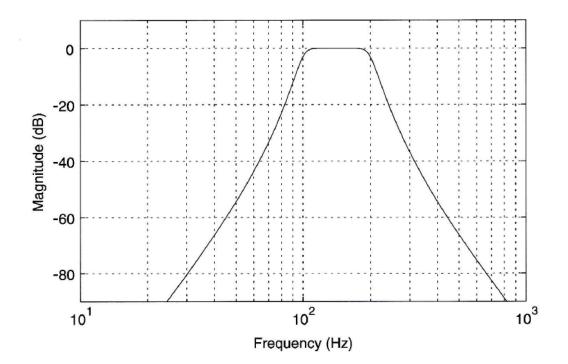

Figure 3.8 shows a band-pass filter magnitude response. As we can see there are two cut-off frequencies, one on the low side and one on the high side. We can get this response by cascading a low-pass and a high-pass filter but it is common to design a single filter with this response.

#### 3.3.1.4 Band-stop or Band-reject Filter

Figure 3.9 shows a band-stop filter magnitude response. Observe that the band-stop filter is the opposite of the band-pass filter. In a band-stop filter a specific range of frequencies is attenu-

ated. The common application of this filter is to reject a specific single frequency rather than a range of frequencies.

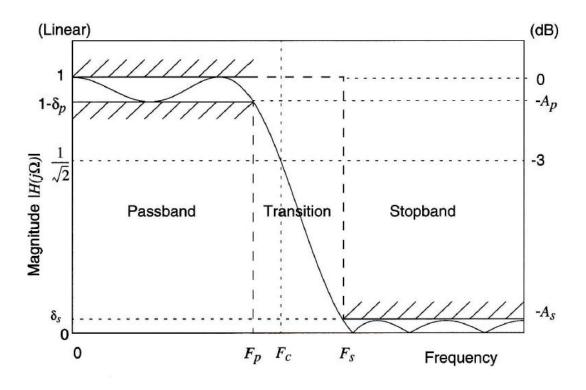

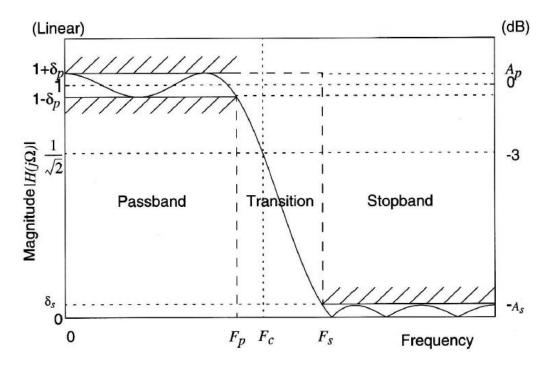

### **3.3.2** Specifying Magnitude Response

Figure 3.10 shows the magnitude response of a low-pass filter with their important characteristics. Also figure 3.11 shows a low-pass filter magnitude response which used to describe digital low-pass filter. The difference between the two magnitude responses is how the allowed variation in the pass-band is described. The first shows a peak to peak variation while the second shows a peak deviation.

The gain of the magnitude frequency response is normalized to 1 (0dB) for a particular frequency depending on the filter type. Also for specifying the magnitude response of a filter we will describe the magnitude response of a low-pass filter.

### 3.3.2.1 Pass-band Cut-off Frequency F<sub>P</sub>

The *pass-band cut-off frequency*  $F_P$  marks the end of the pass-band. Frequencies lower than the cut-off frequency is in the pass-band, and frequencies higher than this are in the transition

Figure 3.6 Magnitude response of low-pass filter

Figure 3.7 Magnitude response of High-pass Filter

Figure 3.8 Magnitude response of Band-pass Filter

Figure 3.9 Magnitude response of Band-stop Filter

band. Note that the cut-off frequency  $F_C$  or -3dB point is in the transition band as shown in figure 3.10.

#### 3.3.2.2 Pass-band Ripple

*Pass-band ripple* is a measure of the allowed variation in magnitude response in the pass-band of the filter [3]. Is often specified in terms of  $\delta_p$  also known as the *pass-band deviation*. As we mentioned in paragraph 3.3.2 there are two different ways of define ripple. Figure 3.10 shows the first which is used for analog filter and figure 3.11 shows the second which is used in digital filter. The first method specifies the maximum deviation measured from a gain of one and is associated with analog filter design [3]. The second method measures the deviation from the ideal pass-band magnitude to the minima and maxima.

The units as shown in figure 3.10 may be in decibels ( $A_P$ ) or linear deviation ( $\delta_p$ ). The relationship between  $A_P$  and  $\delta_p$  depends on the style (analog or digital). The relationship is shown in equations 3.1 and 3.2 for analog and equations 3.3 and 3.4 for digital.

Figure 3.10 Low-pass analog filter parameters

Figure 3.11 Low-pass digital filter parameters

#### 3.3.2.3 Stop-band Ripple

*Stop-band* ripple describes the maximum gain (or minimum attenuation) we want for a signal above the stop-band cut-off frequency. It can be described as either a linear or decibel value. A positive value in decibels like 25 dB should be read as minimum stop-band attenuation, while a negative value should be maximum gain.

#### 3.3.2.4 Stop-band Cut-Off Frequency

As with the pass-band cut-off frequency all the frequencies above this frequency will meet the stop-band ripple tolerance [3]. *Stop-band cut-off frequency* usually abbreviated as  $F_{stop}$  or  $F_s$  (it is not the sampling frequency).

#### 3.3.3 Specifying phase response

If every frequency experiences the same time delay the result will be a linear change in phase. The equation 3.5 describes the relationship between phase ( $\theta$ ), time delay ( $t_d$ ) and frequency ( $\Omega$  radians/sec).

Figure 3.12 shows a linear phase response for a filter. As we can see in the pass-band the phase wraps a few times (jumps of  $2\pi$ ) while in the stop-band has discontinuities in the phase (jumps of  $\pi$ ).

Figure 3.12 Linear phase response of a low-pass filter

Filters with linear phase pass signals without phase distortion. This property is very important in communications, data transmission and other applications where the temporal relationships between different frequency components are important.

#### 3.4 Describing Discrete Time Signals and Systems

As with the continuous time signals there is a frequency domain representation of discrete time signals. Also we can describe discrete time systems in the time domain and frequency domain for which we need the discrete time equivalents of the impulse response and the system function. Before we begin the description of a discrete system in time and frequency domain we need to describe the sampling frequency or sampling rate.

#### 3.4.1 Sampling Frequency

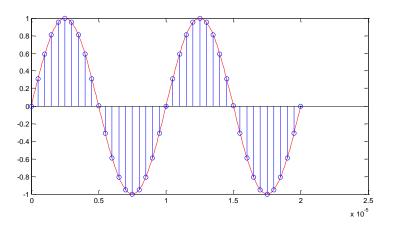

One of the most critical decisions in DSP is choosing the rate at which an analog signal is sampled. This is the *sampling frequency or frequency rate* and usually denoted by  $F_S$  (Hz). The resulting signal which is discontinuous in time is a *Discrete Time Signal*. Figure 3.13 shows an analog signal and the DT signal. From the sampling frequency  $F_S$  we can calculate the *sampling period*  $T_S$  which is  $T_S = 1/F_S$ .

The choice for sampling frequency is depend on the frequency content of the signal to be sampled. Sampling a signal at sampling signal  $F_s$  folds any frequencies higher than FS/2 back into the frequency range of 0 – FS/2. This is known as *aliasing*. Moreover signal components with frequencies higher than FS/2 will produce the same samples as a signal with some frequency in the range 0 –  $F_s/2$  (aliased signal).  $F_s/2$  is known as the *Nyquist frequency* or *folding frequency*. As an example assume a signal at 600Hz and a sampling frequency at 1000 Hz. The signal that produced after the sampling appears to have 400 Hz instead of 600 Hz due to the aliasing.

Figure 3.13 Analog and Discrete time signal

#### 3.4.2 Discrete Time signals in Time and Frequency domain

If x(t) is the continuous signal  $x(nT_s)$  is a discrete time representation where  $n=0,1,2...T_s$  is the sampling period. It is common practice to drop the  $T_s$  which is equivalent to setting the sampling period to 1 sec. Therefore the discrete time sequence is denoted as x(0), x(1), x(2)...

Having set  $T_s$  to 1 sec all the calculations for discrete time signals and systems can be carried out in terms of *normalized frequency*  $\omega$ . The relationship between normalized frequency f and the frequency of the signal F is

The spectrum of a discrete time signal is restricted to a limited range (0 to  $F_s/2$ ) due to the aliasing effects. In terms of normalized frequency  $\omega$  this is the frequency range 0 to  $\pi$  or in terms of f from 0 to 1.

#### 3.4.3 Discrete Time systems in Time and Frequency domain

In paragraph 3.2.1 we discussed that the impulse signal can be used to excite systems at all frequencies. In discrete time systems the impulse response at sample n=0 or the sample at time  $0T_s$  is equal to 1. All other samples have value 0.

Discrete time signals as continuous time signals can be characterized in the frequency domain. The notation that will use is  $H(e^{j\omega})$ , the magnitude  $|H(e^{j\omega})|$  is the gain a signal of frequency  $\omega$  will experience and the angle  $H(e^{j\omega})$  is the phase shift.

#### **3.4.4** The System Function H(z)

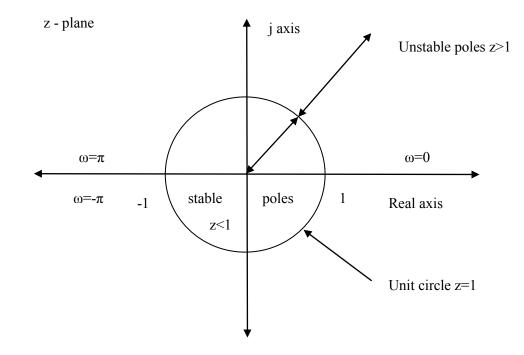

The system function of a discrete time system is H(z). In paragraph 3.2.3 we discussed the system function H(s), the s – plane and the mapping of poles and zeros for a continuous time system. Now in the discrete time systems instead of having s – plane we have the z - plane for mapping the poles and zeros of the system. We will use H(z) to express digital filters because it easily translates to difference equations. Difference equations are used to write the code to perform a digital filter.

The complex variable z is defined in a similar way as the complex variable s of continuous time systems. The difference is that z is defined in terms of polar coordinates rather than rectangular coordinates. Therefore in z – plane we associate angle with normalized frequency  $\omega$  and radical distance with growth/decay.

z is defined as:

Where *r* is the growth/decay factor and  $\omega$  is the angle (in radians). The r is associated with decay if r<1, with growth if r>1 and no change if r=1.

Now we can define the *system function* H(z) for a discrete time system which relates the output Y(z) to the input X(z) of the system. As with H(s), H(z) can be expressed in terms of the ratio of two polynomials:

Figure 3.14 shows the z - plane. In the z - plane the unit circle is the crucial dividing line between stable and unstable poles. Poles inside the unit circle are associated with stable systems while poles outside the unit circle are associated with unstable systems. Poles right on the line are associated with marginally stable systems. Growth and decay is the distance r from the pole. The unit circle has a radius =1

#### **3.4.5** The Difference Equations and H(z)

In paragraph 3.2.3 we determined the H(s) as the Laplace Transform of a system's impulse response h(t). With Laplace transform the differential equations are transformed in H(s) as polynomials which are far easier to use. We have a similar situation with H(z) which is the Discrete Time system function. H(z) is the z – transform of the discrete time impulse response

h(n) [5]. However discrete time systems are not described in terms of differential equations because of their discrete nature they are described by using *difference equations*. The differ-

ence equations express the current output of a system as a linear combination of current input samples, past input samples and past output samples [3]. The most important think is that we can translate these equations into computer programs which used to implement digital filters.

The difference equations have the form:

#### Where

x(0), x(1), x(2), ... is the sequence of input samples

y(0), y(1), y(2), ... is the sequence of output samples

n is the sample index which has values 0, 1, 2, ...

x(n-k) is the kth sample prior to the current sample

y(n-k) is the kth sample prior to the current sample

$b_0$ ,  $b_1$ , ...,  $b_{nz}$  and  $a_0$ ,  $a_1$ , ...,  $a_{np}$  are constant coefficients. Each coefficient may be positive, negative or zero.

$n_z$  is the number of zeros in the system.

$n_p$  is the number of poles in the system.

We must mention that the prior samples are current samples that have been delayed. For example (x-2) was the current value two sample time ago and has been delayed a total of two sample times [3].

The mapping between difference equations and descriptions in the z – domain is equally straightforward. Delays in the difference equation map to multiplication by powers of  $z^{-1}$  in the z-domain. For example x(n) which has no delay is mapped to X(z), but x(n-1) which has a delay of 1 is mapped to  $z^{-1}X(z)$ . In general x(n-k) is mapped to  $z^{-k}X(z)$ .

For example we take a difference equation:

Now we replace each delay by an appropriate power of  $z^{-1}$ , y(n) with Y(z) and x(n) with X(z) so we have the following equation:

Remember that H(z) relates the output to the input (see equation 3.9) and therefore:

Now we can take the z transform of the equation 1.10 as we did above which gives the H(z)

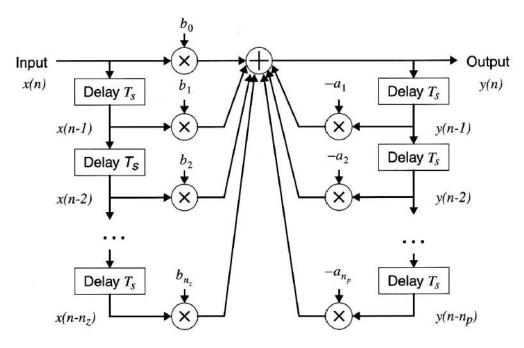

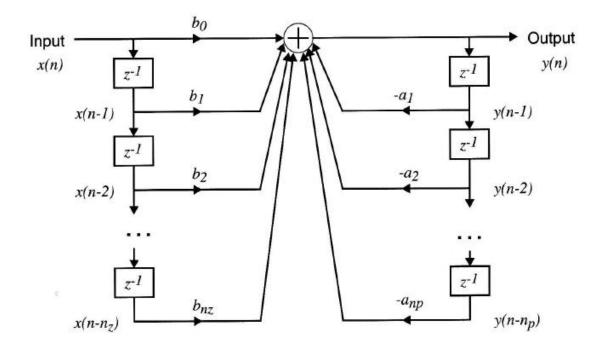

Also from the equation 3.10 we can design the data flow graphically which is shown in figure 3.15 [3].

This type of diagram is used for expressing most digital filter structures and represents the most general class of digital filters.

When at least one of the a<sub>i</sub> values in equation 3.10 is nonzero this class of digital filter is called an *infinite impulse response filter* or *IIR filter*. Figure 3.15 shows the structure of an IIR filter. The name is taken by its impulse response which is infinitely long due to the feedback of its output. Hence IIR filters have both poles and zeros and may be unstable if the poles are not properly located (see figure 3.14). Also they are called recursive filters due to the feedback.

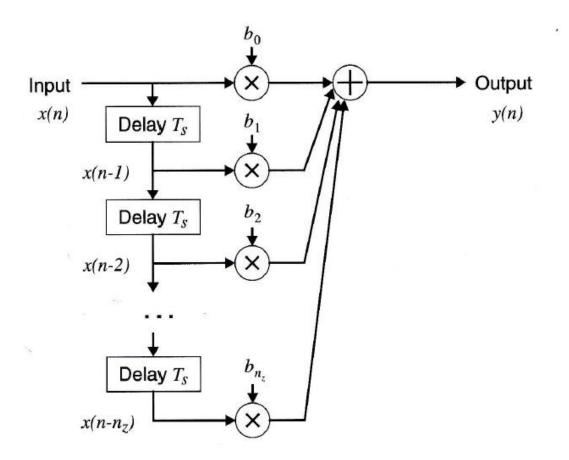

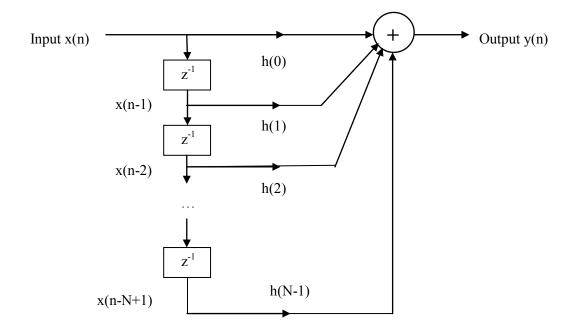

Now a second class of digital filter is possible if the  $a_i$  values are all equal to zero. That mean that there is not feedback and the system has only zeros without poles. This class of filter is called *finite impulse response filter or FIR filter*. Figure 3.16 [3] shows the structure of an FIR filter which is an IIR filter without feedback. Also they are called non recursive filters.

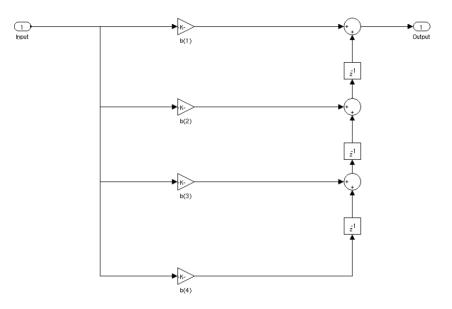

Figure 3.15 IIR filter structure

Figure 3.16 FIR structure

### 3.5 FIR Filters

As the terminology suggests these filters refer to the filter's impulse response. By varying the weight of coefficients and the number of filter taps any frequency response characteristic can be realized with an FIR filter. FIR filters can achieve performance levels which are not possible with analog filters [5]. Generally FIR filters require a large number of multiply-accumulates and therefore require fast and efficient DSPs.

#### 3.5.1 Convolution

In order to understand how FIR filters work we need to mention that FIR filters are Linear and Time-Invariant systems LTI.

Linear systems by definition respond to individual frequency components of signals independently of which other frequencies are present. Scaling (multiplying) the input by some factor scales (multiplying) the output by the same factor. Time-invariant systems respond the same to a signal regardless of when it is present.

As we can see from figure 3.17 the impulse response of an FIR filter is just the sequence of coefficient values one right after another. As the "1" of the impulse travels through the filter

Impulse response (i.e., x(n)=1,0,0, ... for n=0, 1, 2, ...)

|     | x(n) | x(n-1) | x(n-2) |   | x(n-N-2) | x(n-N+1) | y(n)   |

|-----|------|--------|--------|---|----------|----------|--------|

| 0   | 1    | 0      | 0      | 0 | 0        | 0        | h(0)   |

| 1   | 0    | 1      | 0      | 0 | 0        | 0        | h(1)   |

| 2   | 0    | 0      | 1      | 0 | 0        | 0        | h(2)   |

|     | 0    | 0      | 0      |   | 0        | 0        | h()    |

| N-2 | 0    | 0      | 0      | 0 | 1        | 0        | h(N-2) |

| N-1 | 0    | 0      | 0      | 0 | 0        | 1        | h(N-1) |

| N   | 0    | 0      | 0      | 0 | 0        | 0        | 0      |

| N+1 | 0    | 0      | 0      | 0 | 0        | 0        | 0      |

Figure 3.17 Relationship between impulse response and coefficients of an FIR filter

only one coefficient at a time is output. Since FIR filters are linear, if we scale the impulse we input to the system then the output will be a scaled version of the impulse response. Now we can see the input signal (sequence of samples) as just a sequence of scaled impulses each of which produces a scaled and delayed impulse response [3]. Therefore the total output of the filter, should be the impulse response (no delay) scaled by the first sample, added to the impulse response delayed by one sample period and scaled by the second sample and so on. Hence the output of the FIR filter at any given time is the sum of the scaled and delayed impulse response caused by the current and prior input samples. If h(k) is the impulse response

of the filter and N the number of coefficients which is also the length of the filter we can write the following equation:

Mathematically we get the output y(n) by convolving the impulse response with the input signal.

Also we can write that the convolved output y of the linear system is  $y=h^*x$  where h is the impulse response of the filter and x is the input signal (sequence of samples) [5].

For linear time-invariant systems it is sometimes more convenient to express (3.12) in the z-domain with

where H(z) is the FIR's transfer function defined in the z-domain by

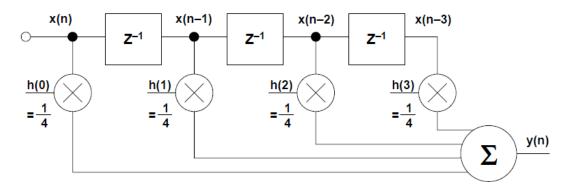

#### 3.5.2 An elementary form of an FIR filter

An elementary form of an FIR filter is shown in figure 3.18 [6]. This elementary form is identical with figure 3.15 which shows the general structure of an FIR filter. The filter has a four tapped delay line (four coefficients) denoted by N. The input samples x(n) are passed through a series of delays which are registers. The registers are labelled as  $z^{-1}$  corresponding to the ztransform representation of a delay element (see paragraph 3.4.5). In the example all the coefficients have the same value which is 0.25. Each sample is multiplied by 0.25 and these results are added to give the output y(n).

Therefore the output y(n) is:

\_

For this filter the output y(n) is:

—

Figure 3.18 A four tapped filter

Since the coefficients are equal there is an easier way to perform the output y(n) as shown in figure 3.19 [6]. The first step is to store the first four samples x(0), x(1), x(2) and x(3) in a register. Then each sample is multiplied by a coefficient, then added together to form the output. Note that the initial outputs y(0), y(1) and y(2) are not valid because all registers are not full until sample x(3) is received. When x(4) sample is received the sample x(0) is subtracted from the result.

| y(3) = 0.25 | x(3) + x(2) + x(1) + x(0) |  |

|-------------|---------------------------|--|

| y(4) = 0.25 | x(4) + x(3) + x(2) + x(1) |  |

| y(5) = 0.25 | x(5) + x(4) + x(3) + x(2) |  |

| y(6) = 0.25 | x(6) + x(5) + x(4) + x(3) |  |

| y(7) = 0.25 | x(7) + x(6) + x(5) + x(4) |  |

Figure 3.19 The output y(n)

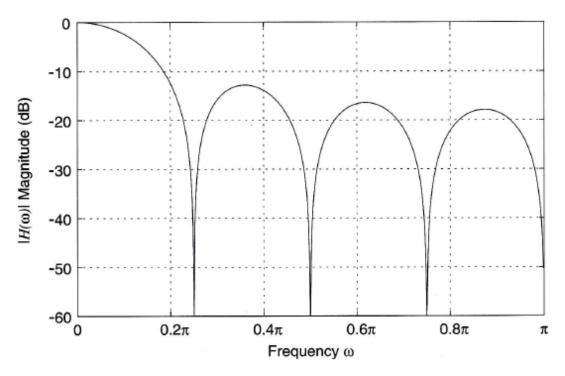

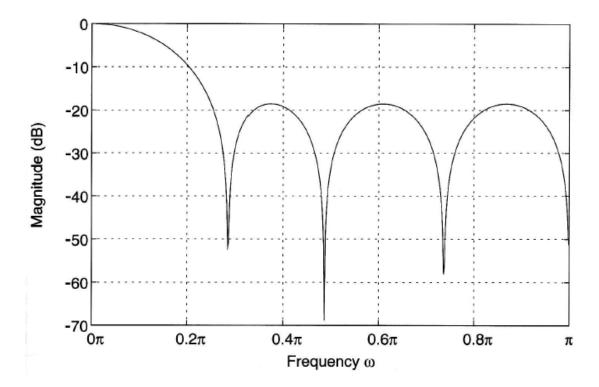

It is possible to improve the performance of this simple FIR filter by properly selecting the individual weights of coefficients rather than giving them equal weight (see figures 3.20 and 3.21). Also the sharpness roll-off of the transition area of the filter can be improved by adding more stages (taps) (see figure 3.22) [6] and the stop-band attenuation characteristics can be improved by properly selecting the filter coefficients. The essence of FIR filter design is the appropriate selection of the filter coefficients and the number of taps to realize the desired transfer function H(f) [6].

Figure 3.20 Magnitude response using equal coefficients

Figure 3.21 Magnitude response using individual weights of coefficients

Figure 3.22 Improvement of sharpness of the roll-off in the transition area

### 3.5.3 Symmetry in FIR Filters

The center of an FIR's impulse response is an important point of symmetry. It is sometimes convenient to define this point as the 0<sup>th</sup> sample instant. Such filter descriptions are a-causal [4]. For an odd-length FIR the a-causal filter model is given by:

Figure 3.23 Symmetry in FIR Filters

#### 3.5.4 Windowing

The idea is to take the ideal frequency response and calculate its impulse response which is the filter coefficients. But a problem arises since the impulse response for a filter with any sharpness to its frequency response is infinitely long. By definition an FIR filter has a limited number of coefficients hence we need to overcome the previous problem. *Windowing* is one way of getting around this problem, hence the name of this technique [6].

In order to understand the windowing first we need to calculate the impulse response for an ideal filter response. The *inverse discrete time Fourier transform IDTFT* is the useful mathematical transform that we can use for converting between the continuous frequency response and the discrete time impulse response. The mathematical definition is:

where  $H(\omega)$  is the discrete-time Fourier transform and h(n) is the impulse response. Using the equation 3.16 we can compute h(n) for the ideal low-pass, high-pass, band-pass and band-stop filter types as shown in table 3.1[3].

| Туре                                                                                            | h <sub>d</sub> (n), n <b>≠0</b>                                 | $h_d(0)$                                                       | $h_d(n)$ |

|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------|----------|

| Lowpass<br>0 ω <sub>c</sub> π                                                                   | $\frac{\sin(n\omega_c)}{\pi n}$                                 | $\frac{\omega_c}{\pi}$                                         |          |

| Highpass                                                                                        | $\frac{-\sin(n\omega_c)}{\pi n}$                                | $1-\frac{\omega_c}{\pi}$                                       |          |

| Bandpass<br>Bandpass                                                                            | $\frac{\sin(n\omega_u)}{\pi n} - \frac{\sin(n\omega_l)}{\pi n}$ | $\frac{\omega_{\mu}}{\pi} - \frac{\omega_l}{\pi}$              |          |

| $ \begin{array}{c} \text{Bandstop} \\ \hline 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\$ | $\frac{\sin(n\omega_l)}{\pi n} - \frac{\sin(n\omega_a)}{\pi n}$ | $1 - \left(\frac{\omega_u}{\pi} - \frac{\omega_l}{\pi}\right)$ |          |

Table 3.1 Ideal impulse responses for common filter types

The infinitely sharp cutoffs of the filters imply a non causal response hence the impulse response extends into positive and negative time. Our filters can deal only with  $n\geq 0$ . Also due the mathematics we need to evaluate separately the cases for n=0.

Figure 3.24 Impulse response of an ideal low-pass filter

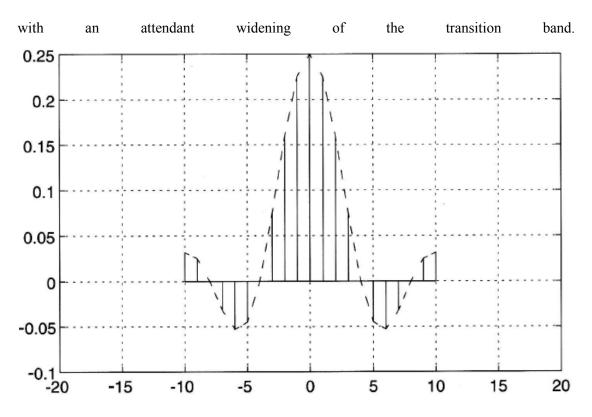

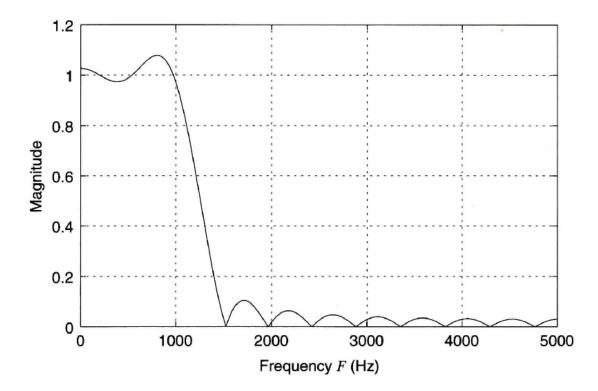

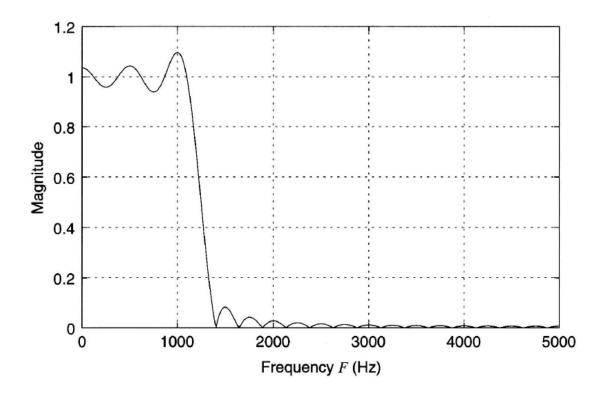

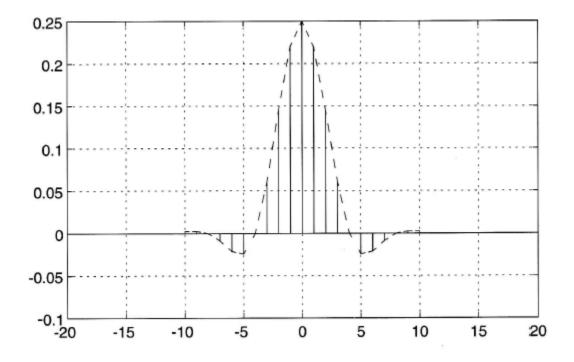

The following diagrams show in figures 3.24 - 3.30 are taken from citation [3]. Figure 3.24 shows the impulse response of an ideal low-pass filter ( $\omega c = \pi/4$ ). Because we need a finite number of coefficients we truncate the impulse response after its get fairly small. Figure 3.25 shows the impulse response after truncating it to 21 points. The corresponding frequency response is shown in figure 3.26 [3]. Now we must observe the "ringing" near the transition frequencies. Can we get rid of that "ringing" by taking more points? Figure 3.27 shows the frequency response using twice as many coefficients as in figure 3.26. Comparing the two figures we can see that although the filter coefficients are essentially increased the ringing at the edge still has about the same quantity. The observed ringing is due to the Gibbs phenomenon which relates to the inability of a finite Fourier spectrum to reproduce sharp edges [7]. The effects of ringing can only suppressed with the use of a data "window" that tapers smoothly to zero on both sides [7]. In figure 3.28 we have taken a special window function and smoothly attenuated our 21 coefficients to zero at both ends. In figure 3.29 we can see that data window-ing overlay the FIR's impulse response, resulting in a smoother magnitude frequency response

Figure 3.25 Truncated ideal low-pass filter impulse response

Figure 3.26 Magnitude response using 21 coefficients

Figure 3.27 Magnitude response using twice as many coefficients as in figure 3.26

Figure 3.28 Smoothing the truncated impulse response.

Figure 3.29 Magnitude response using windowed coefficients

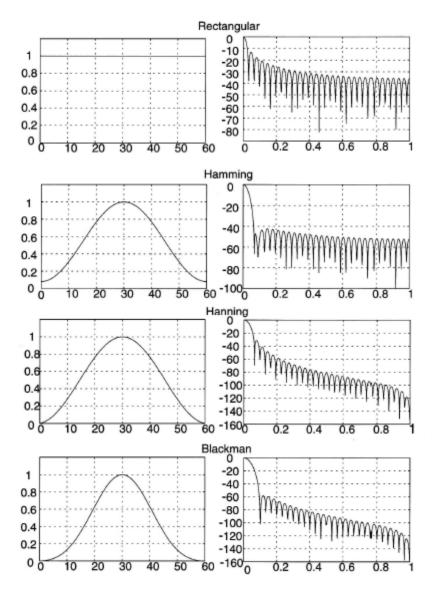

Other classic window functions are summarized in table 3.2 [3]. They differ in terms of their ability to make tradeoffs between "ringing" and transition bandwidth extension. The number of recognized and published window functions is large. The most common windows denoted w(n), are:

- Rectangular: w(n) = 1. This is effectively "no window". Offers the sharpest transition in the frequency domain, but at the expense of lessened attenuation in the stopbands.

- Hanning:  $w(n) = 0.5(1 \cos(2\pi n/N))$ . Much wider transition but with a stop-band attenuation of 30 dB.

- Hamming:  $w(n) = 0.54 0.46\cos(2\pi n/N)$ . A bit wider transition area than Hanning, but an additional 10 dB of stop-band attenuation.

- Blackman: w(n) = 0.42 0.5cos(2πn/N) + 0.08cos(4πn/N). Continuing the trade off of transition width for stop-band attenuation it delivers 74 dB attenuation in the stop-band, but with a transition width is six times bigger than the rectangular window.

- Kaiser: w(n) = - Based on the first order Bessel function  $I_0$  is special in two respects. It is nearly optimal in terms of the relationship between ringing suppression and transition width and second it can be tuned by  $\beta$  which determines the ringing of the filter. This can be seen from the following equation credited to Kaiser.

Where  $A = 20 \log_r is$  both stop-band attenuation and the pass-band ripple in dB. The Kaiser window length to achieve a desired level of suppression can be estimated:

| Window                 | Passpand<br>ripple (dB) | Stopband<br>attenuation<br>(dB) | First side<br>lobe (dB) | Transition<br>width Δf<br>(norm. Hz) |

|------------------------|-------------------------|---------------------------------|-------------------------|--------------------------------------|

| Rectangular            | 0.7416                  | 21                              | -13                     | 0.9/N                                |

| Kaiser, A=30<br>β=2.12 | 0.270                   | 30                              | 19                      | 1.5/N                                |

| Hanning                | 0.0546                  | 44                              | -31                     | 3.1N                                 |

| Kaiser, A=50<br>β=4.55 | 0.0274                  | 50                              | -34                     | 2.9/N                                |

| Hamming                | 0.0194                  | 53                              | -41                     | 3.3/N                                |

| Kaiser, A=70<br>β=6.76 | 0.00275                 | 70                              | -49                     | 4.3/N                                |

| Blackman               | 0.0017                  | 74                              | -57                     | 5.5/N                                |

| Kaiser, A=90<br>β=8.96 | 0.000275                | 90                              | -66                     | 5.7/N                                |

| Table 3.2Key properties of windows | Table 3.2 | Key pr | operties | of windows |

|------------------------------------|-----------|--------|----------|------------|

|------------------------------------|-----------|--------|----------|------------|

Also the time domain and magnitude response of some common windows is shown in figure 3.30.

The key theorem of FIR filter design is that the coefficients h(n) of the FIR filter are the quantized values of the impulse response of the frequency transfer function H(f). Conversely the discrete Fourier transform can be used to transform a digital system's impulse response into its frequency response. Therefore the coefficients of an FIR filter are equivalent to the impulse response of the filter and the output of the filter can be imagined to be the sum of a number of scaled and delayed impulse responses where the scaling is taken from the input signal samples.

Figure 3.30 Time domain and magnitude response of some common windows

### 3.5.5 Structures for FIR Filters

Once the filters coefficients have been determined the next step is to decide on the structure of the filter. From a design perspective linear phase FIR filters have symmetric and antisymmetric coefficients. Depending on the target hardware it may be possible to implement a linear phase FIR filter using less multipliers by taking advantage of the symmetry.

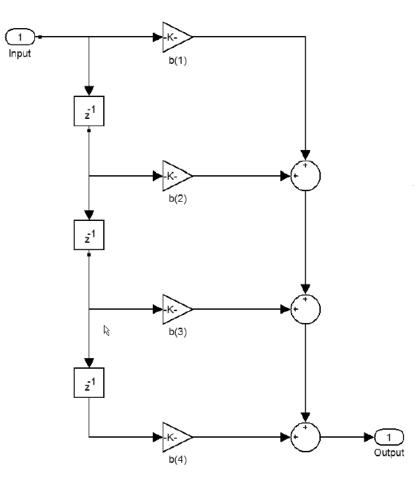

### 3.5.5.1 Direct-form filter structure

The following diagrams show in figures 3.31 - 3.33 was taken from citation [7]. Figure 3.31 shows a 4-tap FIR filter implemented in direct-form. The number of delays is equal to the filter order and the number of coefficients (taps) which is one more than the number of delays determines the filter length [7].

The structure has some regularity in that a sample is read (a delay is a register), multiplied with the filter coefficient, and accumulated to form the output. DSP processors have historically been built with this multiply-accumulate (MAC) instruction in mind [7]. The structure requires a shift of the input data throughout all delays for each sample.

A downside of the direct-form structure is that does not take advantage of the symmetry of the coefficients so the cost is maximum in terms of the number of multipliers required.

Figure 3.31 A 4-tap filter implemented in direct-form

#### 3.5.5.2 Symmetric direct-form filter structure

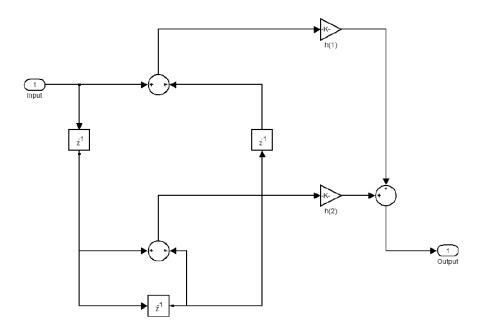

The symmetric direct-form filter structure take advantage of symmetry of the coefficients hence the filter can be implemented with the half number of multipliers than the direct-form filter structure. Figure 3.32 shows a 4-tap symmetric FIR filter using the symmetric direct-form. We must observe that even though there are only two multipliers there are still three delays required (same as the direct-form) since the number of delays corresponds to the filter order.

Figure 3.32 A 4-tap FIR filter using the symmetric direct-form

### 3.5.5.3 Transposed direct-form structure

The direct-form structure has the disadvantage that each adder has to wait for the previous adder to finish before it can compute its result [7]. A solution to this is to use transposed directform structure instead. The benefit of this filter is that we do not need an extra shift register for the input samples, and there is no need for an extra pipeline stage for the adder of the products to achieve high throughput. Figure 3.33 shows a 4-tap FIR filter implemented in transposedform.

Figure 3.33 A 4-tap FIR Filter using the transposed direct-form

### 3.6 IIR Filters

In the previous paragraphs we discussed FIR filters, that they have no feedback and can have only zeros. Also FIR filters have no real analog counterpart. On the other hand IIR filters can have both poles and zeros and have traditional analog counterparts (Butterworth, Chebyshev, Elliptic, and Bessel). Therefore they can be analyzed and synthesized using more familiar traditional design techniques.

Infinite Impulse response Filters get their name because their impulse response extends for an infinite period of time. Although they can be implemented with fewer computations than FIR filters, IIR filters do not much the performance achievable with FIR filters, and do not have linear phase. Figure 3.34 [3] shows a Direct I form of an IIR filter, and writing out the difference equation explicitly shows the feedback of the output into the filter.

Figure 3.34 Direct I form of an IIR filter

The current value of y is based on a weighted sum of current and past values of the input x and of weighted values of the past  $n_p$  values of y. Here  $n_p$  is the numbers of poles and  $n_z$  is the number of zeros [3]. Adding feedback to a digital filter has some effects. For example, for a given magnitude response it is usually for an IIR filter to be 5-10 times shorter (less coefficients) than the equivalent FIR filter. On the other hand the design and the implementation of IIR filters is much less straightforward than for FIR filters. Also IIR filters can never have ab-

solutely linear phase which is a major problem for systems where linear phase is major selling point. In addition there is no computational advantage achieved when the output of an IIR filter is decimated because each output value must always be calculated [3]. The basic characteristics of an IIR filters are:

- Uses feedback

- Impulse response has a infinite duration

- Potentially unstable

- Non linear phase

- More efficient than FIR filters

- No computational advantage when decimating output

# 3.6.1 IIR filter design process

The design process for an IIR filter begins with the same information as that required for FIR filters. The desired behavior of the filter in the frequency domain, usually emphasizing the magnitude response rather than the phase response. Also the presence of feedback means that the filter coefficients and the impulse response are no longer related. Therefore we can't use the same techniques which are used for FIR filters. So a popular method design for IIR filter is to first design the analog equivalent filter and then mathematically transform the transfer function H(s) into the z-domain H(z). This method is called *indirect design method*.

# 3.6.2 Indirect Design Method

Indirect design method produces very efficient IIR filters. As we mentioned above first we must design the analog equivalent filter. The most popular analog filters are the Butterworth, Chebyshev, Elliptical and Bessel and there are many CAD programs available to generate the Laplace transform H(s) for these filters. But the analog filter is only the half of what we need. The key to the indirect method is finding a useful mapping between the analog filters and digital filters, the s to z mapping.

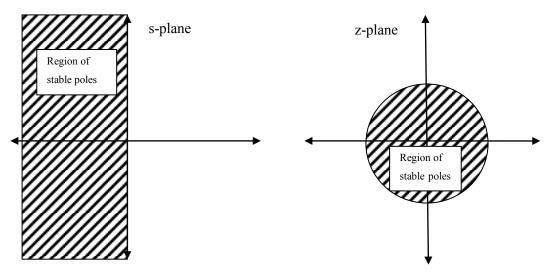

Figure 3.35 shows the regions of stable poles in the s-plane and the z-plane. Remember that the region of the s-plane representing stable poles is the left half plane ( $\sigma$ <0) and the region for stable poles in the z-plane is inside the unit circle. The most popular method which is used for mapping from the s-plane to z-plane is the *bilinear z-transform* (BZT).

Figure 3.35 Regions of stable poles in the s-plane and z-plane

# 3.6.2.1 Analog Filter Prototypes

In this paragraph we will summarize the characteristics of the most popular analog filter prototypes, that is analog filters used as models for the eventual digital filters.

The basic characteristics of a Butterworth filter are:

- The magnitude response in the pass-band is maximally-flat (also the Butterworth filter is called maximally-flat filter).

- The magnitude response in both the pass-band and stop-band is monotonic which is that the magnitude response only decreases or stay the same, as frequency increases.

- Has only poles and no zeros. The poles are evenly spaced along a half circle in the left half s-plane.

The basic characteristics of a Chebyshev I filter are:

- It has ripples which are equal sized in the pass-band

- Monotonic stop-band

- Relatively sharp transition between pass-band and stop-band compared with a Butterworth filter with the same order.

- Have only poles and no zeros. Poles in the s-plane lie on an ellipse and the angles of these poles are the same as those for a Butterworth filter.

- Worse phase shift than Butterworth (non linear near pass-band edge frequency).

The basic characteristics of a Chebyshev II filter are:

- It has ripples in the stop-band which are equal sized.

- Monotonic pass-band.

- Relatively sharp transition between pass-band and stop-band.

- Has poles and zeros. The angles of these poles are the same as those for an equivalent order Butterworth filter but are not at the same locations as for Chebyshev I.

- Worse phase shift than Butterworth (non linear near pass-band edge frequency).

The basic characteristics of the Elliptical filter are:

- It has ripples both in the pass-band and the stop-band.

- Has pole and zeros.

- Sharper transition between pass-band and stop-band than the Chebyshev filter for the same order.

- Even worse phase than Chebyshev I and II.

The basic characteristics of the Bessel filter are:

- No ripples in pass-band and stop-band.

- Is an all pole filter.

- Has maximally linear phase for an IIR filter.

- Has the longest transition region than all the others analog filters for the same number of poles or order.

# 3.6.2.2 Mapping from s to z.

There are three methods used to convert the Laplace transform into the z transform: impulse invariant transformation, bilinear transformation and the matched z-transform. Any method we choose for mapping the s-plane to the z-plane should preserve the crucial elements of the s-plane, including [3]:

- The  $j\Omega$  axis of the s-plane must mup to the unit circle in the z-plane.

- The left half plane of the s-plane must be mapped to the inside of the unit circle of the z-plane.

- Small negative values of σ should map to locations near (but inside) the unit circle (these poles and zeros have the biggest effects on frequency response).

• Large negative values of  $\sigma$  should map locations near the origin of the z-plane (less effect).

# 3.7 FIR versus IIR Filters

Typically IIR filters are more efficient than FIR filters because they require less memory and fewer multiply-accumulate are needed. IIR filters can be designed based upon previous experience with analog filter designs.